Welcome to this informative article where we will explore the concept of Structural Level Modelling in Verilog and its significance in developing precise and efficient digital design skills. As digital design continues to advance, a strong understanding of Verilog and its related methodologies is crucial to excel in this field.

Verilog is a widely used hardware description language (HDL) that enables designers to describe digital circuits in a concise and structured manner. By learning Verilog, designers gain the ability to create complex digital designs and simulate their behavior before actual implementation.

Now, let’s dive into the world of Structural Level Modelling. It involves breaking down large designs into smaller modules, creating a hierarchical structure that simplifies design organization and promotes code reusability. By utilizing Verilog’s structural constructs, designers can connect these modules and create intricate digital circuits.

In our exploration of Structural Level Modelling, we will discuss module instantiation, interconnections between modules, and the use of Verilog’s structural constructs to effectively design complex digital circuits. This practical knowledge will empower digital designers to create scalable and efficient designs.

By adopting Structural Level Modelling techniques, designers can experience numerous benefits. Structured designs are easier to debug, test, and maintain, leading to improved efficiency and productivity. Additionally, the modular nature of Structural Level Modelling allows designs to be easily scaled and modified as project requirements evolve.

Throughout this article, we will provide insights, examples, and best practices to enhance your digital design skills in Verilog. So, join us on this journey to discover the power of Structural Level Modelling in Verilog and unlock your full potential in the realm of digital design.

Table of Contents

Understanding Verilog

Before diving into Verilog’s structural level modelling, it is crucial to develop a solid understanding of Verilog itself. Verilog is a hardware description language (HDL) widely used in digital design.

As a powerful and versatile language, Verilog allows engineers and designers to describe and simulate the behavior of digital circuits. It provides the means to represent the structure and functionality of complex digital systems, using a concise and readable syntax.

Verilog plays a critical role in the design and implementation of digital circuits, enabling engineers to specify the desired behavior of the hardware at a higher level of abstraction. By leveraging Verilog, designers can focus on the functionality and architectural aspects of a circuit, without getting lost in the intricacies of low-level details.

The Role of Verilog in Designing Complex Digital Circuits

Verilog serves as the bridge between the design requirements and the physical implementation of digital circuits. Designers can use Verilog to model a wide range of digital components, including logic gates, multiplexers, adders, memory units, and more.

With Verilog, engineers can create and simulate complex digital circuits before physically implementing them. This allows for effective debugging, ensuring the functionality and correctness of the design even before it reaches the physical hardware stage.

Moreover, Verilog is used in conjunction with simulation tools to verify the performance and timing characteristics of digital systems. Engineers can test and analyze the behavior of their designs under various scenarios, enabling them to identify and rectify any potential issues or bottlenecks early in the development process.

In summary, understanding Verilog is crucial for digital designers as it provides a powerful language to describe, simulate, and verify the behavior of complex digital circuits. By mastering Verilog, designers gain the necessary skills to develop precise and efficient hardware designs.

In the next section, we will explore the concept of structural level modelling in Verilog and its significance in creating modular and scalable designs.

Introduction to Structural Level Modelling

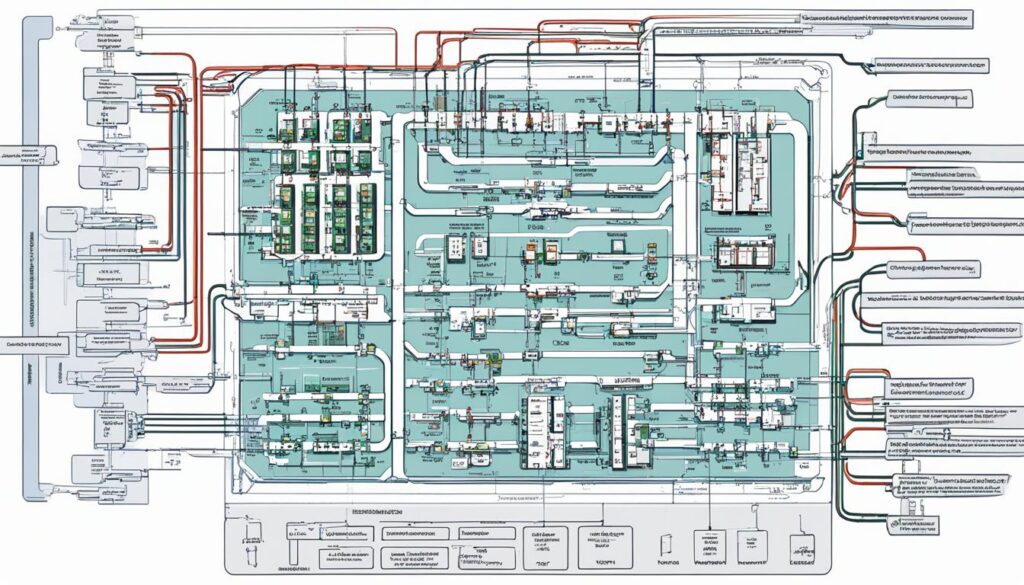

In the world of Verilog development, Structural Level Modelling plays a crucial role in designing precise and efficient digital circuits. This approach involves breaking down complex designs into smaller modules, creating a hierarchical structure in Verilog. Through the use of Verilog modules, designers can organize their code and enhance code reusability.

Structural Level Modelling allows for a systematic approach to digital circuit design, enabling better organization and easier comprehension of complex systems. By dividing the design into smaller modules, each module can be developed and tested individually, simplifying the debugging and testing process.

Through the hierarchical structure created by Structural Level Modelling, the overall design becomes more scalable and adaptable. Changes made to a single module can be propagated throughout the entire circuit, ensuring consistency and reducing the chances of errors.

Implementing Structural Level Modelling also enhances collaboration among designers. With a well-defined modular structure, multiple designers can work simultaneously on different modules, ensuring efficient teamwork.

Let’s take a closer look at the hierarchical structure of Verilog modules in the context of Structural Level Modelling:

Verilog Modules

In Verilog, a module is a self-contained unit that performs a specific function within a larger digital circuit. Each module encapsulates a set of related functionalities while maintaining a clear interface for communication with other modules.

Modules in Structural Level Modelling are developed with reusability in mind. By creating generic and independent modules, designers can easily reuse them in different projects, saving time and effort. Additionally, modules can be easily modified or replaced, providing flexibility in design iterations.

Module instantiation is a fundamental concept in Structural Level Modelling. It refers to the creation of module instances within a higher-level module. These instances act as placeholders for the actual modules, allowing for easy connectivity and integration of different modules.

The interconnections between modules are established using signals, such as wires and buses. Signals carry information between modules, enabling them to exchange data and synchronize their operations. Proper signal naming and assignment are essential for maintaining clarity and avoiding errors.

Implementing Structural Level Modelling with Verilog modules not only enhances the organization and code reusability of digital designs but also facilitates the efficient development of complex circuits. Through the creation of a hierarchical structure, designers can tackle intricate projects with precision and ease, resulting in optimal and robust digital designs.

Next, we will explore the practical aspects of designing with Structural Level Modelling and delve into the module instantiation and interconnections between modules.

Advantages of Structural Level Modelling in Verilog

| Advantages | Explanation |

|---|---|

| Enhanced organization | Breaks down complex designs into modular structures for better management and comprehension. |

| Code reusability | Develops generic modules that can be easily reused in multiple projects, saving time and effort. |

| Scalability | Allows for easy modification and expansion of digital circuits without compromising the overall system. |

| Collaboration | Facilitates teamwork and simultaneous development by providing clear boundaries and interfaces between modules. |

Designing with Structural Level Modelling

Now that we have a solid understanding of Structural Level Modelling in Verilog, let’s dive into the practical aspects of using this technique to design complex digital circuits. In this section, we will explore module instantiation, interconnections between modules, and the effective utilization of Verilog’s structural constructs.

Module Instantiation

Module instantiation is a fundamental concept in Structural Level Modelling. It involves creating instances of Verilog modules within the design hierarchy, allowing for the reuse of existing modules in different parts of the circuit. By instantiating modules, we can build complex circuits by connecting and interconnecting smaller, reusable components.

Let’s consider an example. Suppose we are designing a 4-bit binary adder. Rather than designing the entire adder from scratch, we can instantiate individual modules for the 1-bit full adder and connect them together to create the 4-bit adder. This modular approach not only simplifies the design process but also promotes code reusability and scalability.

Interconnections between Modules

Interconnecting modules is another crucial aspect of designing with Structural Level Modelling. It involves establishing connections and signals between different modules to enable communication and data flow within the circuit.

In our previous example of the 4-bit binary adder, the individual 1-bit full adder modules are connected through carry and sum signals. These interconnections allow the carry out from one adder to propagate to the carry in of the next adder, enabling the addition of multiple bits in parallel.

By carefully planning and implementing interconnections between modules, we can create complex digital circuits with efficient data flow and accurate functionality.

The Power of Structural Constructs in Verilog

Verilog provides powerful structural constructs that enable the seamless implementation of Structural Level Modelling. The language offers various constructs like wires, instances, and signals, allowing us to connect modules and define interconnections easily.

For instance, using the wire data type, we can define interconnecting signals between modules. By instantiating modules and connecting them through these wires, we can create a hierarchical structure in Verilog, resulting in clear and organized code.

Furthermore, Verilog’s structural constructs facilitate code readability, ease debugging, and simplify the verification process. With a well-organized and structured design, it becomes much easier to identify and rectify any issues that may arise during the development stage.

Overall, the effective use of Verilog’s structural constructs, module instantiation, and interconnections between modules empowers designers to create complex and efficient digital circuits.

| Advantages of Designing with Structural Level Modelling |

|---|

| Enhanced Code Reusability |

| Improved Scalability |

| Easier Debugging and Testing |

| Efficient Data Flow |

| Clear Organization and Modularization |

| Simplified Verification Process |

Benefits of Structural Level Modelling

Structural Level Modelling plays a crucial role in the realm of digital design, offering numerous benefits that enhance the efficiency and scalability of designs. By adopting this approach, designers can create precise and well-organized digital circuits, making them easier to debug, test, and maintain.

One of the key advantages of Structural Level Modelling is its ability to improve efficiency in digital design. By breaking down complex circuits into modular structures, designers can optimize individual modules for specific functionalities. This approach simplifies the design process and allows for better utilization of resources, resulting in more efficient and streamlined designs.

Additionally, Structural Level Modelling enables scalability in digital design. The organization of circuits into reusable modules facilitates the development of large and complex systems. Designers can easily modify the connections and interdependencies between modules, allowing for flexibility and scalability without compromising the overall functionality of the design.

Furthermore, Structural Level Modelling enhances the maintainability of digital designs. With a modular structure, debugging and troubleshooting become more manageable. Designers can isolate and analyze specific modules rather than sifting through extensive codebases. This efficient approach saves time and effort, enabling swift identification and resolution of issues.

Ultimately, Structural Level Modelling empowers digital designers to create efficient, scalable, and maintainable solutions. By leveraging its benefits, they can optimize their digital design process and achieve optimal results in terms of performance and reliability.

| Benefits of Structural Level Modelling | Explanation |

|---|---|

| Efficiency | Modular structures optimize individual functionalities, improving overall design efficiency. |

| Scalability | Modules allow for easy modification and expansion, facilitating the development of large and complex systems. |

| Maintainability | Modular structure simplifies debugging and troubleshooting, saving time and effort. |

Conclusion

In conclusion, Structural Level Modelling in Verilog is a powerful technique that enables us to develop precise and efficient digital designs. By organizing complex circuits into modular structures, Verilog allows designers to create scalable and reusable code. This approach enhances the efficiency and scalability of designs, making them easier to debug, test, and maintain.

Understanding and implementing Structural Level Modelling is crucial for enhancing digital design skills and achieving optimal results in the world of Verilog development. By breaking down designs into smaller modules and utilizing Verilog’s structural constructs, designers can create complex circuits with ease. This not only streamlines the design process but also improves code organization and promotes code reusability.

Overall, Structural Level Modelling in Verilog empowers designers to create robust and efficient digital circuits. By leveraging this technique, we can overcome the challenges of complex design projects and produce high-quality solutions. Developing proficiency in Structural Level Modelling is a valuable skill for any digital design professional seeking to excel in Verilog development.