Legalization is key in modern cell placement designs. It makes sure cells are in the right place and don’t overlap. This step is important for keeping the design working well.

It helps make the design better for manufacturing and improves how the chip works. This includes things like timing, power, and design quality.

In ASIC design, legalization is a must during placement, not in floorplanning. The tools handle this step automatically. There are commands to check if the design fits the grid and doesn’t have overlapping cells.

Legalization is vital for cell placement. It makes sure cells don’t overlap, which is good for the design and performance of the chip. It’s a big part of making sure the design works well.

The role of legalization in cell placement is huge. It’s all about making the design better and improving how the chip works. By keeping cells in line and preventing overlaps, legalization helps a lot.

This process is a big part of making ASICs. It has a big impact on how the design works, the chip’s performance, and how it’s made.

Table of Contents

Understanding Cell Placement Fundamentals

Cell placement is key in VLSI design. It involves arranging circuit components on a chip. This process tackles big challenges like cutting down wirelength and improving routability. It also manages temperature.

Floorplanning and detailed placement are crucial steps. They help create a well-designed and efficient integrated circuit.

Basic Components of Circuit Design

At the heart of VLSI design are several basic components. These are essential for the circuit’s structure. They include:

- High Fanout Nets: These are nets that drive many loads, with a maximum per net.

- Macro Padding: It creates space around macros for pin connections to standard cells.

- Scan Chains: These are groups of flip-flops connected through SI/SO pins. They can be reordered to improve routing and reduce congestion.

Role of Cell Arrangement in Chip Design

The way cells are arranged on the chip is vital. It affects the design’s performance and efficiency. Placement aims to optimize area, timing, and power.

The goal is to ensure routability, avoid timing violations, and balance cell and pin density.

Common Placement Challenges

Designers face several challenges during cell placement. These include:

- Congestion: Caused by high pin density, poor macro placements, or bad aspect ratios.

- Timing Violations: These are addressed through High Fanout Net Synthesis and Scan Chain Reordering.

- Aligning with Design Rules: Ensuring standard cells are aligned and spread out in standard cell rows during legalization.

Overcoming these challenges requires a solid grasp of cell placement basics. It also needs knowledge of various techniques and strategies for an optimal solution.

Definition and Purpose of Legalization in Placement

In IC design, legalization is key in the placement stage. It makes sure no cell overlaps and aligns cells to rows. This keeps the design ready for manufacturing and meets performance needs.

The main goal of legalization is to fix the initial placement. It might not follow all rules. Legalization uses methods like diffusion or network flow to move cells to the right spots.

Legalization is a critical step in IC design. It makes sure the design is ready for manufacturing. It optimizes cell alignment and placement, improving the design’s quality.

The legalization process is vital for a manufacturable IC layout. It refines the initial placement and follows design rules. This prepares the design for routing and physical verification, leading to a high-quality IC.

The Physics Behind Cell Movement During Legalization

Legalization is key in cell placement optimization. It uses physics-inspired methods to guide cell migration. One method is the diffusion-based migration process, which models cell movement like physical diffusion.

Diffusion-Based Migration Process

Cells move like particles in a diffusion process during legalization. Their movement is based on the density around them. Cells move from high-density to low-density areas, like molecules do.

Velocity and Density Calculations

The algorithm calculates cell velocity and density at each step. Cells in dense areas move faster to spread out. Density helps find high and low cell areas, guiding migration.

Cell Movement Patterns

This method leads to smooth cell movements. It keeps the original placement’s integrity while legalizing. Cells move gradually, avoiding sudden changes or overlaps. This ensures a balanced and coherent final layout.

The proposed legalization framework outperforms others. It uses diffusion-based cell migration. It shows big improvements in fidelity and reduces spatial violation.

Key Objectives of the Legalization Process

The main goals of the legalization process in integrated circuit design are to cut down total cell displacement and reduce half-perimeter wirelength (HPWL). It also aims to keep or boost timing optimization and routability. Finding a balance between these goals is key to getting high-quality placement results.

Modern legalization algorithms work to improve chip performance. They focus on optimizing multiple objectives at once. This includes power distribution and overall design quality improvements.

Legalization algorithms aim to enhance chip performance by getting better results in HPWL, total, and maximum displacements. Studies have shown that fast legalization algorithms can significantly reduce wirelength and displacement. They have also shown big improvements in HPWL, total and maximum displacements, and running time.

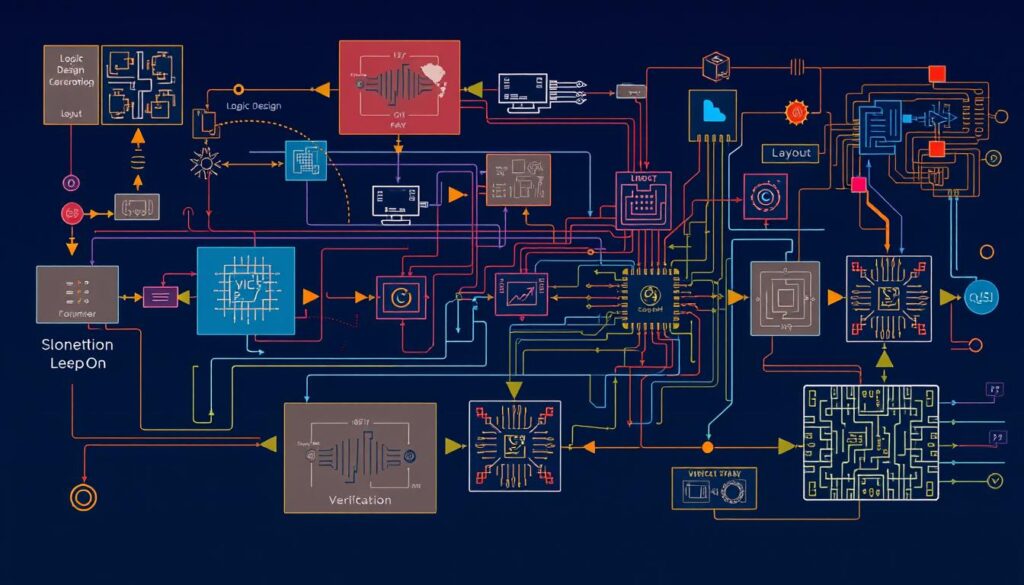

The legalization process is a vital part of the physical design flow. It includes global placement, legalization, and detailed placement. Good legalization strategies aim to minimize displacement and wirelength. They also ensure cells are aligned within defined row constraints.

Fast row selection techniques and accurate linear wirelength models are crucial for efficient legalization. They help achieve optimal chip performance and placement quality.

Source Links

- [SOLVED] – Regarding placement legalization in cadence

- Placement

- PLACEMENT – VLSI TALKS

- Placement Overview – VLSITutor

- PLACEMENT

- ASIC Backend Design Flow in VLSI (Part-3) : Placement and Routing (PnR)

- Quantum Legalization and Detailed Placement for Superconducting Quantum Computers

- Algorithm Selection Framework for Legalization Using Deep Convolutional Neural Networks and Transfer Learning

- A Connectivity-Based Legalization Scheme for Standard Cell Placement

- US7934188B2 – Legalization of VLSI circuit placement with blockages using hierarchical row slicing

- Fast Legalization for Standard Cell Placement with Simultaneous Wirelength and Displacement Minimization

- Exploiting Net Connectivity in Legalization and Detailed Placement Scenarios