Clock Tree Synthesis (CTS) is a key method in VLSI design. It spreads clock signals evenly across a chip’s sequential parts. Its main goal is to cut down on clock skew and delay, making sure the clock signal arrives on time everywhere.

CTS does this by adding buffers and inverters along the clock paths. This meets the needed skew and latency standards.

Getting clock distribution right is essential for modern circuits. It affects the chip’s performance, power use, and size. CTS is a vital step in the design process, after Placement and before Routing. It builds and balances the clock tree using structures like Fishbone, H-tree, and X-tree.

The role of Clock Tree Synthesis is huge. It tackles big challenges like clock latency, skew, and power use. By managing these, CTS boosts the chip’s quality and ensures it meets timing and power needs.

Table of Contents

Understanding Clock Distribution in Modern Digital Circuits

Modern digital circuits use synchronous designs. They rely on registers or flip-flops that change data in sync with the clock signal. This clock signal is like blood flow, crucial for a chip’s performance, power, and area (PPA) metrics.

The Role of Clock Signals in Synchronous Designs

Clock signals start at the source and reach all sink pins. These include registers, latches, and macro clock pins. The goal is to use less routing and meet timing needs.

Impact on Performance, Power, and Area (PPA)

The clock network design is key. It improves system performance by using average delays. It also affects memory, logic, and clocking circuitry for better performance and reliability.

Clock Signal Flow from Source to Sinks

Clock networks have memory, logic, and clocking parts. They are vital for performance and reliability. Designing the network can also reduce sensitivity to process variations, improving performance.

| Clock Tree Routing Algorithms | Key Features |

|---|---|

| H-Tree | Designed for scenarios where clock terminals are arranged symmetrically, like in gate arrays in FPGAs. |

| X-Tree | Similar to H-Tree but with non-rectilinear connections, potentially causing crosstalk due to wire proximity. |

| Method of Mean and Median (MMM) Algorithm | Follows a strategy akin to the H-Tree algorithm but allows sink locations at any point on the chip surface, leading to non-rectilinear clock routing. |

| Recursive Geometric Matching (RGM) Algorithm | Utilizes a bottom-up approach for clock tree construction, achieving zero skew by determining minimum cost geometric matching of sink nodes. |

Algorithms like H-Tree, X-Tree, MMM, and RGM aim to minimize skew. They ensure clock paths are equal in length for optimal signal timing.

Clock Tree Synthesis Fundamentals

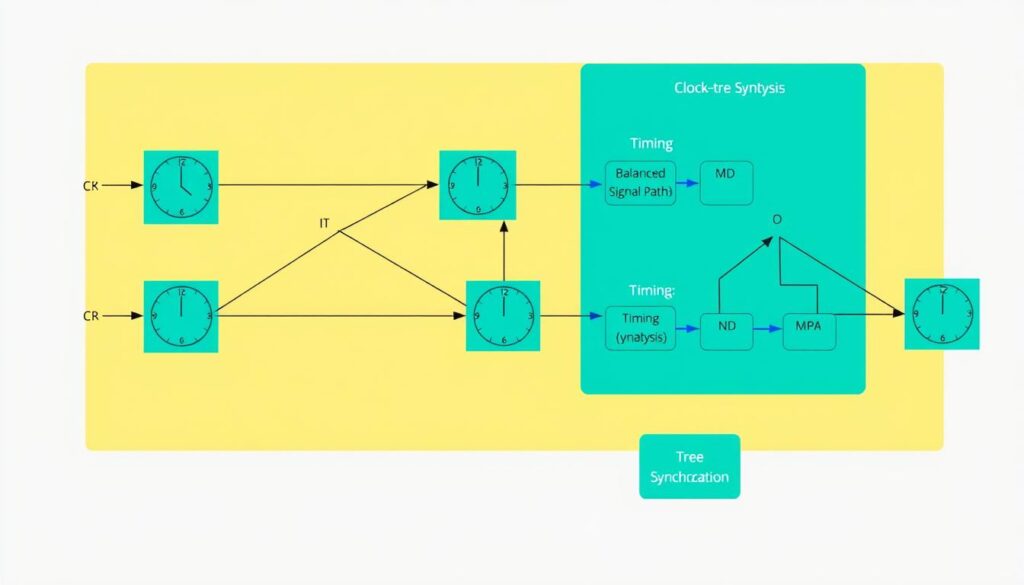

The CTS (Clock Tree Synthesis) process is key in digital circuit design. It ensures the clock signal is evenly distributed and load balance is managed. The journey begins with clustering, where skew groups are formed based on component locations.

Then, DRV (Design Rule Violation) fixing addresses issues like maximum transition time and capacitance. This step also looks at maximum length and fanout.

Insertion delay and power reduction are vital in the CTS process. Balancing is done using clock buffers and inverters. More inverters are often used in practice.

Post-conditioning checks and fixes the clock tree’s integrity. This ensures the clock tree meets quality standards.

Quality checks in CTS include reducing insertion delay and skew balancing. It also focuses on maintaining duty cycle and pulse width. Managing power consumption and addressing signal integrity and crosstalk are also key.

The CTS process is crucial for high-performance, low-power, and reliable clock distribution. It ensures digital circuits operate efficiently and reliably.

| CTS Process Step | Description |

|---|---|

| Clustering | Creating skew groups based on component locations |

| DRV Fixing | Addressing issues related to max_tran, max_cap, max_length, and max_fanout |

| Insertion Delay Reduction | Minimizing clock path delays |

| Power Reduction | Optimizing clock tree power consumption |

| Clock Tree Balancing | Using buffers and inverters to balance the clock tree |

| Post-conditioning | Final DRV checks and fixes |

The CTS process is essential for high-performance, low-power, and reliable clock distribution. It ensures proper clock balancing, skew reduction, latency management, and overall clock tree quality. Designers can optimize the CTS process to meet today’s complex digital system requirements.

Key Parameters and Quality Metrics in CTS

Clock Tree Synthesis (CTS) is key in digital circuit design. It ensures clock signals are distributed well. Engineers focus on several important parameters to make designs better, faster, and more reliable.

Clock Latency and Skew Management

Clock latency is how long it takes for a clock signal to reach its destination. Keeping this low is vital for design synchronization. Clock skew, or the time difference between clock arrivals at different points, also needs to be controlled. Both local and global skew affect design performance and stability.

Transition Time and Slew Rate Control

The transition time, or slew rate, of the clock signal is crucial. A high transition time can cause more power use and timing problems. Designers must adjust this time to meet the needs of all sequential elements in the design.

Power Consumption Considerations

Power use is a big concern in circuit design, and the clock network often uses the most power. Using clock gating and multi-bit registers can lower clock tree power use without hurting performance. Analyzing the clock tree’s power use is key for an energy-efficient design.

| Metric | Desired Outcome | Impact on Design |

|---|---|---|

| Clock Latency | Minimize arrival time at sinks | Maintains synchronization across design |

| Clock Skew | Tight control of local and global skew | Ensures design stability and performance |

| Transition Time | Optimize for minimal power dissipation | Meets timing requirements of sequential elements |

| Power Consumption | Reduce through clock gating and multi-bit registers | Achieves energy-efficient design |

By managing these key parameters, designers can make clock distribution networks better. These networks are crucial for the success of modern digital circuits.

Clock Tree Architectures and Implementation

There are different architectures for clock tree synthesis (CTS) in digital circuits. The single-point CTS is best for low-frequency tasks because it uses less power. Yet, it can cause bigger local skew issues.

The clock mesh is great for fast processors because it balances well. But, it uses more power. To find a middle ground, the multi-source CTS (MSCTS) combines different clock sources. This helps manage power and skew better.

The H-tree algorithm is also key for balancing the clock tree. It divides the area into smaller parts to reach all clock pins effectively.

Building the clock tree involves several steps. These include clustering, fixing DRV, reducing insertion delay, and balancing. The tree is split into top, trunk, and leaf parts for better analysis and optimization.

Source Links

- What is Clock Tree Synthesis?

- Ultimate Guide: Clock Tree Synthesis – AnySilicon

- Clock Tree Synthesis in VLSI Physical Design

- Clock Tree routing Algorithms

- Clock Tree 101 – Timing Basics

- Clock distribution networks in synchronous digital integrated circuits – Proceedings of the IEEE

- CTS (CLOCK TREE SYNTHESIS) – VLSI TALKS

- Clock Tree Synthesis – VLSITutor

- A Clock Tree Synthesis Flow Tailored for Low Power

- clock tree quality – Digital Implementation – Cadence Technology Forums

- Clock Tree Synthesis.pdf

- Clock tree synthesis and SoC clock distribution strategies

- Clock Tree Synthesis – SignOff Semiconductors

- Addressing Clock Tree Synthesis Challenges