At our company, we are constantly exploring ways to optimize chip performance and efficiency. One technique we rely on is called time borrowing, which is widely used in static timing analysis (STA). Time borrowing allows us to improve the overall timing of the paths in a chip by leveraging the property of latches.

When a path ends at a latch, it can borrow time from the next path in the pipeline, ensuring that the timing remains the same. By strategically utilizing time borrowing, we can enhance chip performance and efficiency.

In this article, we will delve deeper into the concept of time borrowing, its benefits, and its application in latch-based designs. We will also explore the advantages of latch-based designs over flip flop-based designs, and how time borrowing can be utilized effectively.

Table of Contents

Latches vs. Flip Flops: Understanding the Difference

In the world of sequential circuits, latches and flip flops are two common types of storage elements. They play a crucial role in maintaining and transferring data within digital systems. Understanding the differences between latches and flip flops is essential for designing efficient and reliable circuits.

Latches: Level-Sensitive and Asynchronous Devices

Latches are level-sensitive devices that operate asynchronously. They are transparent in nature, which means their output immediately reflects any changes in the input signal. Latches are built using basic logic gates such as AND, OR, and NOT. These gates control the flow of data, allowing it to propagate through the latch circuit.

Latches are commonly used in scenarios where real-time data processing is critical. They can be found in applications such as digital signal processing, memory storage, and data synchronization. However, their level-sensitive nature can make them susceptible to glitches and timing hazards.

Flip Flops: Edge-Triggered and Synchronous Devices

Flip flops, on the other hand, are edge-triggered devices that operate synchronously with respect to a clock signal. They change state only when the active edge of the clock signal is triggered. This provides synchronized control over the data transfer process, enabling precise timing and reliable operation.

Flip flops are usually constructed using latches. This combination allows for the storage of data and controlled release based on clock edge triggers. Every flip flop consists of a storage element, which can be a latch, and a clocked element, which enables the data transfer based on clock transitions.

Flip flop-based designs are widely used in digital systems due to their synchronous nature. They are commonly employed in applications such as microprocessors, memory units, and sequential logic circuits. However, the inclusion of flip flops increases design complexity, as they require careful management of clock skew and timing considerations.

When comparing latches and flip flops, it’s important to consider key factors such as clock signal requirements, timing constraints, and the complexity of the circuit design. Latch-based designs offer simplicity, better variation tolerance, and improved yield. They also operate faster and consume less power compared to flip flop-based designs. However, flip flops provide precise control over data transfer and are essential in applications that require synchronized operation.

To summarize, latches and flip flops are fundamental components of sequential circuits. While latches are level-sensitive and asynchronous devices, flip flops are edge-triggered and synchronous devices. Both have their strengths and weaknesses, and choosing between them depends on the specific requirements of the digital system being designed.

The Advantages of Latch-Based Designs

In latch-based designs, we can leverage the benefits of shorter delay paths to compensate for longer combinational delays, resulting in improved overall performance. By utilizing latch-based designs, we can also take advantage of time borrowing, a technique that allows longer paths to borrow time from shorter paths. This ensures that the overall timing of the design is maintained, effectively eliminating timing violations and optimizing the utilization of available time.

Latch-based designs offer several advantages over flip flop-based designs. Firstly, they enable us to overcome the limitations imposed by longer combinational delays. Rather than encountering timing violations, latch-based designs can efficiently compensate for these delays by borrowing time. This ability to adjust timing dynamically contributes to better chip performance.

Additionally, latch-based designs exhibit enhanced tolerance to process variations. Process variations can lead to discrepancies in the performance and functionality of integrated circuits. By using latch-based designs, we can mitigate the impact of these variations, resulting in better yield and increased reliability of the chip.

Overall, latch-based designs offer higher performance and efficiency when compared to flip flop-based designs. Their ability to compensate for longer combinational delays and adapt to process variations makes them a preferred choice for optimizing chip performance and ensuring reliable operation.

Understanding Time Borrowing in Latch-Based Designs

In the realm of latch-based designs, an essential technique called time borrowing plays a significant role in optimizing chip performance. Time borrowing allows a longer path within the design to borrow time from a shorter path, enabling the compensation of delays and ensuring the overall timing of the paths remains consistent. This technique proves invaluable in scenarios where combinational logic delays pose potential timing violations.

When designing latch-based circuits, the ideal scenario entails data launched from one latch reaching the next latch at the next active clock edge. However, if the combinational logic delay is large, timing issues may arise. Latches provide an effective solution by allowing data to wait at the D pin of the latch until the data from the previous latch arrives, facilitating time borrowing and ensuring timing requirements are met.

The concept of time borrowing hinges on the principle that, under certain conditions, data can be launched within a latch even if it arrives after the ideal clock edge. This borrowed time ensures that the data effectively reaches the subsequent components of the circuit, sidestepping potential setup violations. By leveraging time borrowing, designers can optimize performance and maintain the desired timing characteristics of their latch-based designs.

Benefits of Time Borrowing in Latch-Based Designs

Time borrowing represents a powerful optimization strategy within latch-based designs, offering numerous benefits:

- Compensation of Path Delay: By borrowing time from shorter paths, latch-based designs effectively compensate for longer combinational path delays, enabling the design to meet timing requirements.

- Enhanced Clock Period: Time borrowing allows for the optimization of the clock period by mitigating the impact of longer path delays, thereby improving the efficiency and performance of the circuit.

- Optimal Use of Combination Logic: Through time borrowing, latch-based designs ensure the efficient utilization of combination logic, effectively managing path delays and reducing the potential for timing violations.

By maximizing the benefits of time borrowing, designers can unlock the full potential of latch-based designs, achieving superior chip performance and optimization.

Example of Time Borrowing in Latch-Based Designs

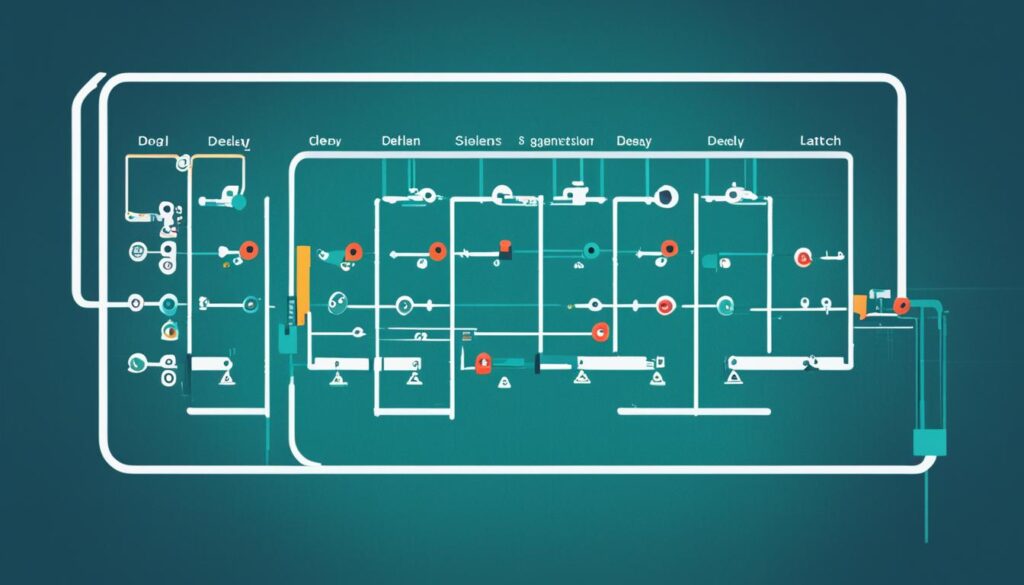

Let’s consider an example where two flip flops are connected by a combinational logic block with a delay greater than the clock period. Without time borrowing, this scenario would result in a setup violation.

| Without Time Borrowing | With Time Borrowing |

|---|---|

| The delay of the combinational logic exceeds the clock period, leading to a setup violation | Replacing one flip flop with a latch enables time borrowing, allowing for the launch of data even if it arrives after the ideal clock edge. This borrowed time ensures that the data reaches the subsequent flip flop on time, avoiding setup violations. |

Through the strategic application of time borrowing, designers ensure that their latch-based designs maintain timing integrity, enabling the unhindered propagation of data within the circuit.

Examples of Time Borrowing in Latch-Based Designs

Time borrowing in latch-based designs can be demonstrated through practical examples, highlighting its effectiveness in addressing setup violations and optimizing chip performance. Consider a scenario where there are two flip flops with a combinational logic delay that exceeds the clock period. This situation would typically lead to a setup violation, jeopardizing the integrity of the design. However, by replacing one of the flip flops with a latch, time borrowing can be harnessed to overcome this challenge.

When a latch is introduced, it provides a crucial window of time during which data can be launched, even if it arrives after the ideal clock edge. This borrowed time ensures that the data reaches the subsequent flip flop on time, effectively bypassing the setup violation. The latch acts as a buffer, allowing data to wait at its D pin until the data from the previous latch arrives, thus maintaining the required timing alignment.

Furthermore, in circuits with multiple latches and complex combinational logic paths, time borrowing can be leveraged to compensate for delays and uphold the overall timing requirements. By carefully coordinating the use of latches and optimizing the distribution of delays, designers can ensure that the critical paths in the circuit meet the necessary timing constraints, resulting in improved performance and reliability.

By harnessing the power of time borrowing in latch-based designs, designers can unlock potential optimizations that enhance chip performance and efficiency. The ability to compensate for longer combinational path delays by borrowing time from shorter paths ensures that the design meets timing requirements, ultimately leading to better overall circuit performance and functionality.

Timing Borrowing: Benefits and Considerations

Timing borrowing is a crucial technique in latch-based designs that offers several benefits. By leveraging timing borrowing, designers can compensate for longer combinational path delays by borrowing time from shorter paths. This allows the design to meet timing requirements and ultimately leads to improved performance and efficiency.

In latch-based designs, the ability to borrow time between paths enables designers to optimize the chip’s performance. By allowing longer paths to borrow time from shorter paths, designers can effectively balance the delays and ensure that the overall timing of the design is maintained. This technique proves particularly useful when faced with longer combinational path delays, as it allows designers to offset those delays with shorter paths, thereby maintaining the required timing.

It’s important to note that timing borrowing is limited to latch-based designs and may not be applicable in flip flop-based designs. Latches provide the necessary flexibility to facilitate the borrowing of time, whereas flip flops operate on clock signals and do not offer the same capability.

When considering the implementation of timing borrowing techniques, several factors must be taken into account. The clock period, for instance, influences the maximum borrow time available for the design. Designers must ensure that the borrowing of time is within safe limits to avoid timing violations. Additionally, the path delays within the design must be carefully analyzed to identify suitable opportunities for timing borrowing.

Let’s take a closer look at the benefits and considerations of timing borrowing in latch-based designs:

Benefits of Timing Borrowing:

- Compensation of longer combinational path delays

- Improved performance and efficiency

- Optimized chip performance

Considerations for Successful Timing Borrowing:

- Applicable only in latch-based designs

- Ensure clock period allows for safe borrowing of time

- Analyze path delays to identify suitable opportunities

By carefully considering these benefits and considerations, designers can effectively leverage timing borrowing in latch-based designs to enhance the chip’s performance and meet timing requirements.

| Timing Borrowing | Latch-Based Designs | Clock Period | Performance | Path Delays |

|---|---|---|---|---|

| Benefits | Optimized chip performance | Improved performance and efficiency | ||

| Considerations | Applicable only in latch-based designs | Ensure safe borrowing of time | Analyze path delays |

Interconnect Delay Models and Maximum Clock Frequency

When designing circuits, understanding interconnect delay models is crucial for optimizing chip performance and meeting timing requirements. These models take into account factors such as wire load and delay, which directly impact the overall timing and performance of the circuit.

By accurately analyzing and modeling interconnect delays, designers can determine the maximum clock frequency at which the circuit can operate while maintaining timing integrity. This maximum clock frequency is a critical parameter in chip design, as it directly influences circuit performance and functionality.

Timing analysis plays a key role in calculating the maximum clock frequency. This analysis involves evaluating the delays introduced by the interconnection of various circuit components and how these delays affect the signal propagation throughout the circuit.

Timing analysis helps identify potential timing violations and ensures that the circuit’s timing requirements are met. By identifying critical paths and understanding the interconnect delay models, designers can make informed decisions to optimize circuit performance.

Let’s take a closer look at an example of how interconnect delay models and timing analysis impact circuit performance:

Example: Maximum Clock Frequency Calculation

In a circuit with multiple components interconnected by wires, each wire introduces a certain amount of delay. This delay can vary based on factors such as wire length, capacitance, and resistance.

To calculate the maximum clock frequency, designers analyze the delay introduced by each wire and determine the critical path with the longest delay. The critical path represents the path with the highest delay and determines the overall performance of the circuit.

By calculating the delay of the critical path and considering the setup and hold times of the flip flops or latches used in the circuit, designers can determine the maximum clock frequency at which the circuit can operate reliably without violating the timing requirements.

Interconnect Delay Models and Circuit Performance

The interconnect delay models provide valuable insights into circuit performance. They help designers identify potential bottlenecks and areas for improvement, enabling them to optimize the design for better performance and efficiency.

By analyzing interconnect delay models, designers can make informed decisions regarding wire routing, component placement, and signal integrity considerations. This ensures that the circuit operates at its maximum potential and meets the desired performance requirements.

Furthermore, understanding interconnect delay models allows designers to identify optimizations and trade-offs in terms of circuit performance. For example, by reducing the length of critical interconnects or optimizing wire width, designers can minimize signal degradation and improve overall performance.

Summary

In conclusion, interconnect delay models play a vital role in determining the maximum clock frequency of a circuit. By accurately analyzing these models and performing timing analysis, designers can optimize chip performance and ensure that timing requirements are met.

Understanding the interconnect delay models allows for informed decisions regarding wire routing, component placement, and signal integrity considerations. By leveraging this knowledge, designers can optimize circuit performance and achieve higher levels of efficiency.

Stay tuned for the next section, where we will delve into advanced techniques for timing analysis and circuit optimization.

Conclusion

In conclusion, time borrowing is a powerful technique in latch-based designs that allows for the compensation of longer path delays by borrowing time from shorter paths. By understanding the differences between latches and flip flops, we can make informed decisions to leverage the benefits of latch-based designs and incorporate time borrowing to meet timing requirements. This optimization technique significantly improves chip performance and efficiency, leading to better overall circuit performance and functionality.

With accurate timing analysis and optimization, designers can enhance chip performance and ensure that the timing requirements are met. By implementing latch-based designs and utilizing time borrowing, we can effectively address longer combinational path delays and maintain the overall timing of the design. This approach not only improves chip performance but also increases efficiency, allowing for better utilization of available time.

Overall, time borrowing in latch-based designs offers a valuable solution for optimizing chip performance and achieving efficient circuit operation. By integrating this technique into the design process and considering the various factors such as chip performance and optimization, designers can create high-performing chips that meet the demands of modern technology.