In this section, we will introduce the concept of assertions in Verilog and discuss their critical role in ensuring robust digital circuit design and flawless hardware behavior.

As digital circuit designers, we understand the importance of creating circuits that not only function correctly but also exhibit reliable behavior. Verilog, a hardware description language, allows us to specify the behavior of digital circuits at a higher level of abstraction. However, as designs become increasingly complex, it becomes essential to verify the correctness of our circuit designs.

This is where assertions come in.

Assertions in Verilog serve as powerful tools that enable us to define properties and conditions that must hold true during the operation of a digital circuit. By incorporating assertions into our design and verification process, we can identify and rectify potential design issues early on, ensuring that our circuits meet the desired specifications.

Table of Contents

What are Assertions in Verilog?

Assertions play a crucial role in the design and verification process of digital circuits implemented in Verilog. In this section, we will define assertions in Verilog and explain their purpose in ensuring the correctness and reliability of hardware behavior.

An assertion in Verilog is a statement or condition that is checked during the simulation or formal verification of a digital circuit design. It serves as a powerful tool for designers to specify and enforce certain properties or behaviors expected from the hardware implementation.

The main purpose of assertions in Verilog is to validate the functionality and behavior of a digital circuit design. By providing a set of logical constraints and checks, assertions allow designers to detect and uncover potential issues or errors that may arise during the operation of the circuit.

Through the use of assertions, designers can specify requirements that must be met by the circuit design, ensuring that it operates within predefined boundaries and adheres to specific rules. This helps in identifying and eliminating design flaws and preventing unexpected behaviors that could lead to system failures or malfunctions.

Furthermore, assertions aid in the debugging process by providing valuable insights and diagnostic information when issues are encountered. By triggering alerts or notifications when certain conditions are violated, assertions can help pinpoint the root cause of problems and guide designers in rectifying them.

In the next section, we will explore the different types of assertions in Verilog, including immediate assertions and concurrent assertions. We will also discuss the usage of system functions and system tasks in constructing assertions.

Types of Assertions in Verilog

In Verilog, there are various types of assertions that play a critical role in validating the behavior and functionality of digital circuit designs. Understanding these different types is essential for designers looking to ensure the correctness and reliability of their designs.

Immediate Assertions

Immediate assertions in Verilog are used to make instantaneous checks on signals and variables during simulation. They are written using the $assert system task and allow designers to specify conditions that should be met at specific points in time. Immediate assertions are useful for catching errors and anomalies early in the simulation process, helping to identify potential design flaws.

Concurrent Assertions

Concurrent assertions, on the other hand, provide a means to specify properties that should hold true throughout the entire simulation. They are written using the assert statement and enable designers to define complex conditions and behavior for signals, modules, or the entire design. Concurrent assertions are particularly valuable for formal verification, as they allow for exhaustive checking of design properties.

System Functions and System Tasks

Verilog also provides system functions and system tasks that can be utilized in constructing assertions. System functions, such as $rose and $fell, enable designers to check for specific signal transitions or levels within the assertions. System tasks, such as $display or $error, allow for displaying or reporting information during simulation. These system functions and tasks enhance the flexibility and functionality of assertions in Verilog.

By leveraging the different types of assertions, including immediate assertions and concurrent assertions, and utilizing system functions and system tasks, designers can comprehensively verify the behavior and performance of their digital circuit designs implemented in Verilog.

Next, we will delve into the syntax and usage of assertions in Verilog, further exploring how they can be effectively utilized in design and verification processes.

Syntax and Usage of Assertions in Verilog

Assertions in Verilog provide a powerful means of specifying desired circuit behavior, aiding in the verification process and ensuring the correctness and reliability of hardware designs. In this section, we will explore the syntax and usage of assertions in Verilog, discussing the property specification language and various assertion constructs.

Writing Assertions Using the Property Specification Language

In Verilog, assertions are written using the property specification language. This language allows designers to express desired circuit behavior using assertion constructs that capture specific conditions and properties. By defining these properties, we can verify the correctness of our designs and ensure they behave as intended.

Let’s take a look at an example to better understand the syntax of the property specification language:

“`verilog

assert property (@(posedge clk) disable iff(rst_n) (a && b) || (c && d));

“`

In the example above, we have a property that is triggered on the positive edge of the clock signal (`posedge clk`) and is disabled when the reset signal is active (`rst_n`). The property specifies that either the signals `a` and `b` should both be true, or the signals `c` and `d` should both be true.

Exploring Assertion Constructs

Verilog provides a range of assertion constructs that allow designers to specify different types of properties and conditions. Some commonly used assertion constructs include:

| Construct | Description |

|---|---|

| `$past` | Specifies the value of a signal in the previous clock cycle. |

| `$rose` | Triggers when a signal transitions from low to high. |

| `$fell` | Triggers when a signal transitions from high to low. |

| `$stable` | Triggers when a signal remains stable for a specified duration. |

These constructs, along with many others, allow designers to specify intricate timing and behavior constraints in their assertions, enabling thorough verification of their designs.

Summary

In this section, we explored the syntax and usage of assertions in Verilog. We discussed writing assertions using the property specification language and explored various assertion constructs. By utilizing these constructs effectively, designers can specify desired circuit behavior and ensure the correctness of digital designs in Verilog.

Verifying Design with Assertions in Verilog

In the process of designing digital circuits in Verilog, it is crucial to ensure the correctness and functionality of the design. This is where assertions play a vital role. By using assertions, designers can verify and validate their designs, identify potential issues, and validate specific conditions or behaviors within the circuit implementation.

Role of Design Verification

Design verification is an essential step in the design cycle, and assertions are an integral part of this process. Verification aims to confirm that the design meets its intended functionality and adheres to the desired specifications.

Assertions aid in the design verification process by providing a concise and formal way to specify expected system behavior. By incorporating assertions into the design, designers can define properties that must hold true during simulation or formal verification, allowing them to catch and debug errors more efficiently.

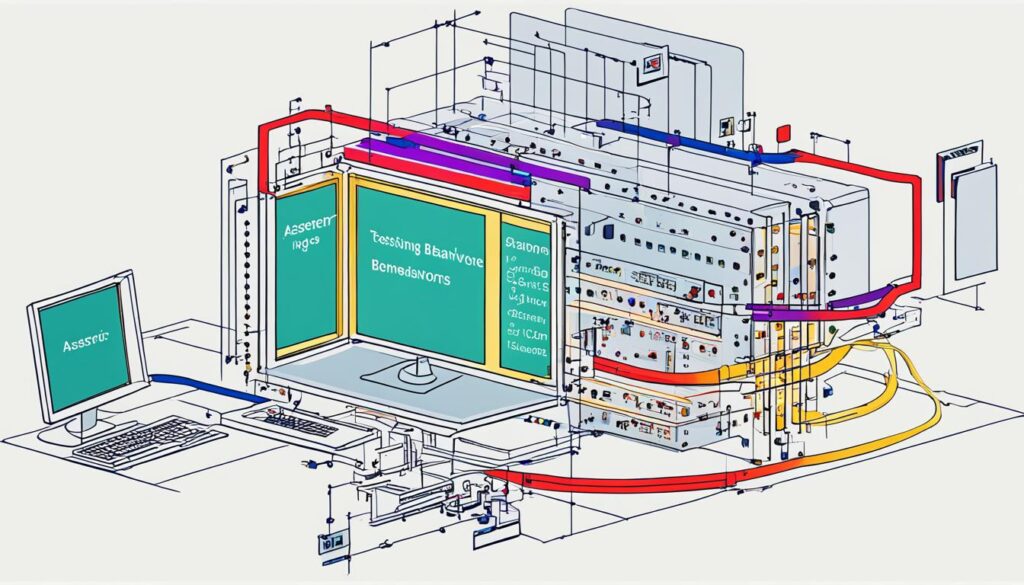

Simulation-based Verification

Simulation is a widely used method for verifying digital circuit designs in Verilog. During simulation, stimulus is applied to the design and its behavior is observed. By defining assertions within the testbench, designers can verify that the design satisfies specific conditions, ensuring that it performs as intended.

For example, an assertion can be written to check if the output of a circuit matches the expected result for a given input. If the assertion fails, it indicates a discrepancy between the expected behavior and the actual behavior, helping designers identify and fix potential design issues.

Formal Verification with Assertions

Formal verification complements simulation-based verification by using mathematical techniques to prove or disprove specific properties of a design. Assertions play a significant role in formal verification, allowing designers to express properties that the design must satisfy.

During the formal verification process, a mathematical model of the design is created, and assertions are used to specify the desired properties. The formal verification tool then analyzes the design and verifies if the properties hold true for all possible inputs and states of the design. If an assertion fails to hold, it indicates a design flaw that needs to be addressed.

Identifying and Resolving Design Issues

Assertions serve as a powerful debugging tool during the design verification process. By defining assertions that capture the expected design behavior, designers can quickly identify deviations and pinpoint potential bugs or flaws.

When an assertion fails, it provides valuable information about the specific condition or behavior that violated the expected property. This helps designers narrow down the potential sources of the issue, enabling them to focus their debugging efforts and resolve the problem efficiently.

Through the combined use of simulation-based verification and formal verification, along with well-crafted assertions, designers can gain confidence in the correctness and reliability of their Verilog designs.

Conclusion

In conclusion, assertions play a crucial role in ensuring the reliability and functionality of digital circuit designs implemented in Verilog. By utilizing assertions effectively, designers can identify and address potential issues early in the design process, resulting in improved hardware behavior and greater design confidence.

Assertions, as a cornerstone of Verilog, enable designers to specify desired circuit behavior and verify its correctness. By defining properties and constraints, designers can thoroughly test their designs, detect bugs, and ensure the desired behavior of their digital circuits. This proactive approach not only saves time but also enhances the overall quality of the design.

The integration of assertions within the Verilog design flow empowers engineers to make informed decisions during the development process, maximizing productivity and minimizing risks. By leveraging the power of assertions, designers can confidently validate their designs, troubleshoot potential issues, and optimize performance.