Welcome to our comprehensive guide on the syntax and structure of Verilog. In this article, we will explore the fundamental aspects of Verilog, including its syntax, structure, and basic principles. Understanding these basics is crucial for anyone looking to master hardware design and simulation using Verilog.

Verilog is a hardware description language used for designing and modeling digital systems. It provides a concise and powerful way to describe complex hardware behavior and interconnections. With Verilog, you can design everything from simple logic gates to advanced processors and complex systems.

Before diving into Verilog modules and other advanced concepts, it is important to have a solid grasp of the language’s syntax and structure. This foundation will serve as a building block for your future Verilog designs.

Throughout this article, we will cover various topics, starting with the basic syntax of Verilog. We will discuss how Verilog code is structured, the different components it consists of, and the rules you need to follow to ensure correct syntax. By mastering the syntax, you will be able to write clean and efficient Verilog code.

Next, we will move on to Verilog modules and their hierarchical structure. We will explore how to define modules, instantiate them, and establish a hierarchical design to create complex systems. This understanding will allow you to break down your designs into manageable modules while maintaining the overall system integrity.

We will then delve into Verilog data types and variables. Understanding and effectively using data types and variables in Verilog is crucial for implementing the desired functionality in your hardware designs. We will explore the different data types available and learn how to declare and use variables effectively.

Another important aspect we will cover is Verilog procedural blocks and control statements. These constructs enable you to implement decision-making and repetitive behaviors in your Verilog designs. We will discuss how to use if-else statements, for loops, and other control structures to create dynamic and responsive systems.

In conclusion, this article aims to provide you with a solid understanding of the basic syntax and structure of Verilog. By familiarizing yourself with Verilog modules, data types, variables, procedural blocks, and control statements, you will be well-equipped to design and simulate hardware systems using Verilog. Let’s embark on this Verilog journey together and unlock the potential of hardware design!

Table of Contents

Verilog modules and hierarchy

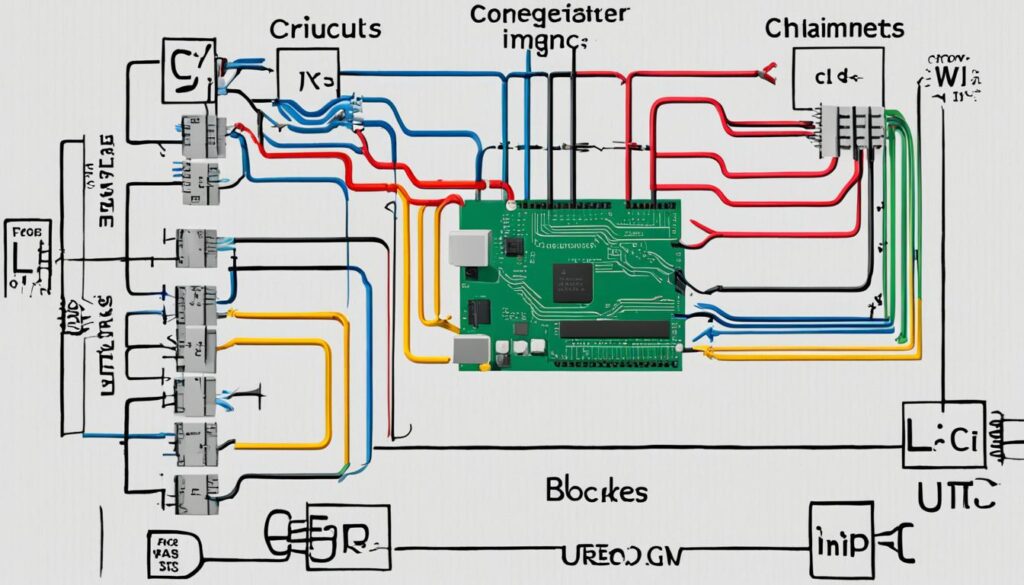

In this section, we will explore the concept of Verilog modules and their hierarchical structure. Understanding how to define and use Verilog modules is crucial for creating complex hardware systems. By leveraging module instantiation and establishing a hierarchical design, we can effectively organize our Verilog code and enhance the scalability and reusability of our hardware designs.

Defining Verilog Modules

Verilog modules are blocks of code that encapsulate a specific functionality or component within a hardware system. These modules serve as building blocks for our designs, allowing us to break down complex systems into smaller, more manageable components. By modularizing our code, we can improve readability, maintainability, and ease of debugging.

To define a Verilog module, we use the module keyword, followed by the module name and a list of input and output ports. Each port is associated with a specific signal or data connection that allows communication between different modules or components of the system.

Instantiating Verilog Modules

Once we have defined a Verilog module, we can instantiate it within another module or at the top level of our design. This process involves creating an instance of the module and connecting the input and output ports to the appropriate signals or data paths.

Module instantiation allows for a hierarchical design approach, where we can build complex systems by connecting and interconnecting different modules. This hierarchical structure promotes modularity, reusability, and efficient design organization.

Establishing a Hierarchical Design

In Verilog, a hierarchical design refers to the arrangement of modules in a structured and organized manner. By breaking down a system into smaller, self-contained modules, we can create a hierarchical structure that reflects the system’s functional hierarchy.

This hierarchical design approach offers several advantages. It enables parallel development of different modules by different team members, promotes code reuse, simplifies debugging and testing, and facilitates system integration.

By carefully designing and structuring our Verilog code using modules and establishing a hierarchical structure, we can achieve highly efficient and scalable hardware designs. This approach enhances code readability, minimizes complexity, and allows for seamless collaboration within a team working on the same project.

| Advantages of Verilog Modules and Hierarchy |

|---|

| Enhanced code readability |

| Easier code maintenance and debugging |

| Improved scalability and reusability |

| Promotes parallel development and code reuse |

| Simplifies system integration |

Verilog data types and variables

In Verilog, data types and variables play a crucial role in designing and modeling hardware systems. Understanding how to declare and use variables effectively is essential to the success of your Verilog projects. In this section, we will explore the various Verilog data types and learn how to work with variables.

Verilog Data Types

Verilog provides several data types that allow you to represent different kinds of information in your hardware designs. These data types include:

- Bit – represents a single binary value (0 or 1).

- Integer – represents a signed or unsigned whole number.

- Real – represents a real number with decimal points.

- Reg – represents a register that can store binary values.

- Wire – represents connections between different modules.

- Enum – represents a set of named values.

- Array – represents a collection of elements of the same data type.

Each data type has its own purpose and usage in Verilog, allowing you to model and simulate hardware systems with precision and accuracy.

Declaring Variables in Verilog

To use data types effectively, you need to declare variables in Verilog. Variable declaration allows you to allocate memory and define the properties of the variable, such as its name, data type, and initial value.

Here’s an example of declaring a variable in Verilog:

integer count; // declares an integer variable named 'count'

bit [7:0] data; // declares an 8-bit vector variable named 'data'

reg [3:0] enable = 4'd7; // declares a 4-bit register variable named 'enable' with an initial value of 7By declaring variables, you can store and manipulate data within your Verilog designs. Variables allow you to represent and simulate real-world behavior, making your hardware models more dynamic and versatile.

Now that we understand the importance of data types and variable declaration in Verilog, let’s put them into practice in our hardware designs.

Verilog procedural blocks and control statements

In this section, we will explore the powerful features of Verilog procedural blocks and control statements that enable us to implement decision-making and repetitive behaviors in our designs.

Verilog Procedural Blocks

Verilog allows us to define procedural blocks within our code to group related statements together. Procedural blocks provide a structured way to control the flow of execution based on specific conditions or events. The most commonly used procedural block in Verilog is the always block, which executes its statements whenever certain conditions are met or events occur.

Consider the following example:

always @(posedge clk)

begin

if (reset)

counter In this code snippet, the always @(posedge clk) block is triggered on the positive edge of the clock signal. Inside the block, we use an if-else statement to increment the counter variable by 1 if the reset signal is not active. Otherwise, we reset the counter to 0.

Verilog Control Statements

Verilog provides several control statements that allow us to structure our code and control the flow of execution based on specific conditions. These control statements include the if-else statement, the for loop, and the case statement.

The if-else statement allows us to make decisions and execute different sets of statements based on certain conditions. Here’s an example:

if (condition)

begin

// Statements to execute when the condition is true

end

else

begin

// Statements to execute when the condition is false

end

The for loop allows us to repeat a set of statements for a specified number of iterations. Here’s an example:

for (initialization; condition; increment/decrement)

begin

// Statements to execute in each iteration

end

The case statement allows us to select a set of statements to execute based on the value of a variable or an expression. Here’s an example:

case (value)

value1: begin

// Statements to execute when value equals value1

end

value2: begin

// Statements to execute when value equals value2

end

default: begin

// Statements to execute when none of the cases match

end

endcase

By utilizing these Verilog control statements, we can create complex decision-making and repetitive behaviors that are essential for designing efficient and functional hardware systems.

Conclusion

In conclusion, we have explored the basic syntax and structure of Verilog, an essential language for hardware design. By understanding the Verilog modules, data types, variables, procedural blocks, and control statements, you will have gained the necessary knowledge to design and simulate complex hardware systems effectively.

Mastering Verilog syntax is crucial for hardware designers as it forms the foundation for creating robust and efficient designs. With Verilog’s hierarchical structure, you can build complex systems by dividing them into smaller modules, enabling easier design reuse and maintenance.

Moreover, by utilizing Verilog’s wide range of data types and variables, you can create flexible and adaptive designs that meet the specific requirements of your hardware projects. Verilog’s procedural blocks, along with control statements like if-else and for loop, allow you to implement decision-making logic and repetitive behaviors, adding dynamic capabilities to your designs.

In summary, a solid understanding of Verilog syntax and structure is crucial for successful hardware design. By using Verilog effectively, you can create efficient and reliable hardware designs, ensuring optimal performance in various electronic systems.