Welcome to our comprehensive guide on module definition in Verilog. In this article, we will delve into the intricacies of designing Verilog modules, providing you with the knowledge and skills to create robust and efficient Verilog designs. Whether you are a beginner or an experienced Verilog programmer, understanding module definition is essential for successful Verilog programming.

Throughout this guide, we will cover everything from the basic concept of a Verilog module to the structure of a module, designing modules, instantiating modules, and using parameters and generics. By the end, you will have a solid understanding of how to effectively design and structure Verilog modules for your projects.

But before we dive into the details, let’s take a moment to understand what a Verilog module is and its importance in Verilog design.

Table of Contents

What is a Verilog Module?

In Verilog design, a module is a fundamental building block that encapsulates a specific functionality or behavior within a digital circuit. It serves as a self-contained unit that can be instantiated and interconnected with other modules to create a complete system. A Verilog module provides a high-level representation of hardware components, allowing designers to encapsulate complex logic and easily reuse it in their designs.

At its core, a Verilog module represents a digital component, such as a flip-flop, arithmetic unit, memory element, or any other hardware function. It consists of inputs, outputs, and internal logic that defines its behavior. To create a Verilog module, we must define its interface, specify the input and output signals, and describe the internal implementation of the logic.

Verilog modules are essential for modular and hierarchical design. By breaking down complex systems into smaller, reusable modules, we can improve the readability and maintainability of our Verilog code. Modules allow us to divide the design into manageable parts, making it easier to debug, test, and modify specific functionality without affecting the entire system.

When designing a Verilog module, it’s crucial to follow a standardized module structure that adheres to industry best practices. This ensures consistency across designs and facilitates collaboration among designers. A well-defined Verilog module enhances code readability, simplifies documentation, and promotes code reuse, making it an integral part of efficient Verilog design.

Functionality and Reusability

A significant advantage of using Verilog modules is their inherent functionality and reusability. Once a module is designed, it can be instantiated multiple times within a design, enabling us to create complex circuits without duplicating code. This modular approach not only saves development time but also allows us to optimize performance by carefully designing and reusing efficient modules.

Encapsulation of Logic

A Verilog module encapsulates its internal logic, shielding it from the rest of the design. This encapsulation helps manage complexity and promotes code organization. Each module focuses on a specific functionality, making it easier to understand and maintain. By abstracting the internal workings of a module, we can treat it as a black box, simplifying the design process and providing modularity.

Furthermore, encapsulation allows us to make changes to the internal logic of a module without affecting the rest of the design. This modularity enables us to iterate and optimize individual modules independently, enhancing overall design efficiency.

In the next section, we will delve into the structure of a Verilog module and explore the various components that make up a module’s definition.

Structure of a Verilog Module

A Verilog module is composed of various elements that collectively define its structure. Understanding these components is essential for designing and implementing Verilog modules effectively. In this section, we will explore the different aspects of a Verilog module, including module ports, input and output signals, and their connections.

Module Ports

Module ports serve as the interface between the module and the outside world. They define the input and output connections of the module, allowing it to communicate with other modules or the main design. Each port represents a specific signal or data flow, and it must be properly declared and connected for the module to function correctly.

Verilog modules can have multiple input and output ports, enabling complex interactions between different parts of a design. The module ports are declared within the module definition using the appropriate syntax, specifying the direction (input or output) and data type of each port.

Input and Output Signals

Input signals are used to provide data or control information to a Verilog module. These signals are typically connected to external components or other modules and can be used as inputs for computations or logical operations within the module.

On the other hand, output signals represent the results or outputs of the module’s operations. They convey processed data, status information, or any other relevant output to the outside world. Output signals are connected to the inputs of other modules or interface with the main design as required.

The declaration of input and output signals is essential for the proper functioning and connectivity of a Verilog module. By specifying the data type, size, and direction of these signals, the module designer ensures compatibility and seamless integration with other parts of the design.

Defining and Connecting Signals

In Verilog, signals are defined using the appropriate data type and size. This ensures that the signals can represent the desired data accurately. Each signal should have a unique name to avoid conflicts or confusion within the module or design hierarchy.

To establish connections between modules, the input and output signals of different modules must be connected properly. This is done by explicitly specifying the connections in the module instantiation statement or using a higher-level design hierarchy. Proper signal connection is crucial for the correct flow of data and functionality between modules.

By understanding the structure of a Verilog module, including module ports, input and output signals, and their connections, we can effectively design and implement modules that seamlessly integrate into larger Verilog designs. The next section will focus on best practices for designing Verilog modules, including hierarchical designs and reusable modules.

Designing a Verilog Module

When it comes to Verilog programming, designing a module is a crucial aspect. A well-designed Verilog module can greatly impact the overall performance and reusability of your code. In this section, we will discuss the best practices for designing Verilog modules, including the use of hierarchical modules and creating reusable modules.

Hierarchical Modules

One of the key principles in Verilog module design is the use of hierarchical modules. Hierarchical modules allow you to create a modular and organized structure for your code, making it easier to understand and maintain. By breaking down complex designs into smaller, more manageable modules, you can improve readability and simplify troubleshooting.

When designing hierarchical modules, it is important to carefully consider the functionality and interconnections between modules. Plan out the hierarchy based on the logical structure of your design, ensuring that each module has a clear purpose and well-defined inputs and outputs. This will promote modularity and facilitate code reuse, enabling you to efficiently build complex systems.

Reusable Modules

Creating reusable modules is another essential practice in Verilog module design. By designing modules that can be easily reused in multiple projects, you can save time and effort in future developments. To create reusable modules, it is important to focus on abstraction and encapsulation.

Abstraction involves creating modules that perform specific functionalities without exposing unnecessary implementation details. This allows other designers to use the module without needing to understand its internal workings, promoting code reuse.

Encapsulation entails bundling related functionality and data together within a module, protecting the internal details from external interference. By encapsulating logic and data within modules, you can prevent unintended modifications and minimize the potential for errors.

To further enhance reusability, consider parameterizing your modules. For example, you can use parameters to create generic modules that can be easily customized for different applications. This flexibility enables you to create configurable modules that adapt to various design requirements.

Optimizing Module Performance

When designing Verilog modules, it’s important to consider performance optimization. Optimizing module performance can help enhance the overall efficiency and speed of your design.

One way to optimize module performance is to minimize the propagation delay within the module. By reducing the delay of critical paths and minimizing redundant logic, you can improve the overall speed of your design. This involves carefully analyzing the timing paths within the module and making appropriate design choices, such as reducing the number of levels of logic or using faster components.

Another aspect to consider is power optimization. Power consumption is a critical factor in many electronic systems, and optimizing module design can help reduce power consumption. Techniques such as clock gating, power gating, and voltage scaling can be used to minimize power consumption without sacrificing performance.

Overall, designing a Verilog module involves careful planning, utilizing hierarchical structures, creating reusable modules, and optimizing performance. By following these best practices, you can ensure that your Verilog modules are well-structured, reusable, and achieve optimal performance for your designs.

Instantiating Verilog Modules

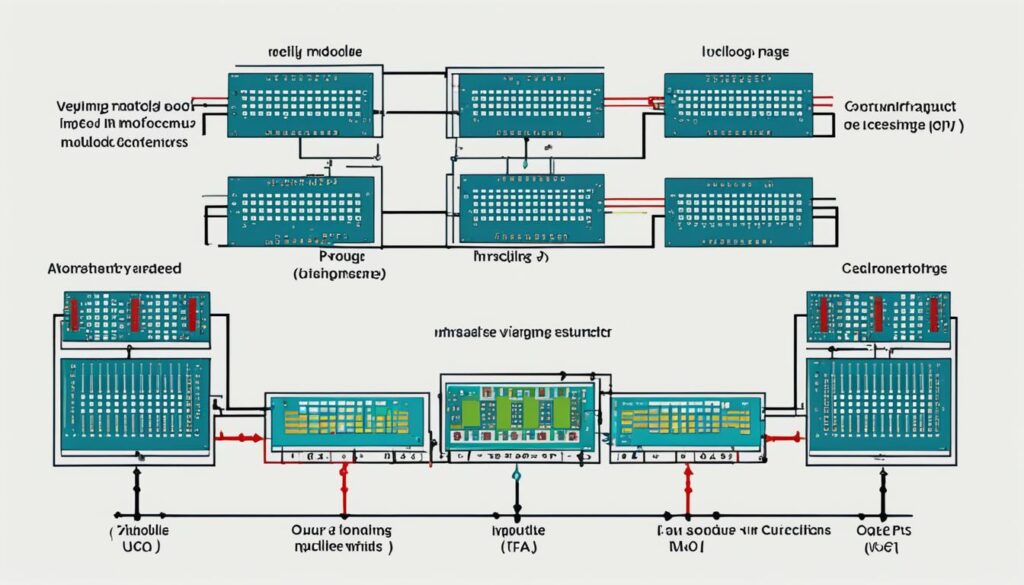

In Verilog, module instantiation plays a crucial role in creating a modular and hierarchical design. It allows us to reuse existing modules and build complex systems by interconnecting these modules. In this section, we will explore the process of instantiating Verilog modules, managing the module hierarchy, and establishing connections between modules.

Instantiating a Verilog module involves creating an instance of the module within another module or at the top level of the design. It allows us to incorporate the functionality of a module into a larger system. To instantiate a module, we need to specify the module name, the instance name, and link the module’s input and output ports to the signals in the design.

Module Instantiation Syntax

The syntax for module instantiation in Verilog is as follows:

module instance_name ( .port_name1(signal_name1), .port_name2(signal_name2), ... );The ‘instance_name‘ is the name given to the instance of the module, and it can be used to refer to the module instance within the design. The ‘port_name‘ represents the name of the port in the module definition, and the ‘signal_name‘ represents the corresponding signal in the design. Multiple ports and signals can be connected using a comma-separated list.

Let’s consider an example where we have a module called ‘adder’ defined as follows:

module adder (input a, input b, output sum);

// Adder implementation code

endmoduleTo instantiate the ‘adder’ module and connect its ports, we can use the following syntax:

adder adder_instance (.a(signal_a), .b(signal_b), .sum(signal_sum));In the above example, ‘adder_instance‘ is the name given to the instance of the ‘adder’ module. ‘signal_a‘, ‘signal_b‘, and ‘signal_sum‘ are signals within the design that are connected to the input and output ports of the ‘adder’ module.

Managing Module Hierarchy

When instantiating multiple modules, it is important to manage the module hierarchy effectively. The module hierarchy defines the relationship between modules and their instances. It determines the flow of signals and the organization of the design.

A well-structured module hierarchy enhances readability, reusability, and maintainability of the design. It allows for better organization and simplifies debugging and troubleshooting.

When designing the module hierarchy, consider the functional blocks of the design and the interactions between them. Identify the major components or modules and their relationships. Create instances of modules within other modules to form a hierarchical structure, clearly representing the flow of signals and data.

Establishing Module Connections

The connections between modules are established through the instantiation process. The signals in the design are connected to the ports of the instantiated modules.

To establish module connections, ensure that the signals and ports have the same data type and size. This ensures proper communication and data transfer between the modules. Incorrectly connected signals can lead to simulation errors and unexpected behavior in the design.

When connecting the signals to the module ports, ensure correct ordering and mapping. The order of the signals in the instantiation statement should match the order of the ports in the module definition. Use named connections to avoid errors due to incorrect ordering.

By effectively instantiating Verilog modules, managing the module hierarchy, and establishing proper connections between modules, we can create modular designs that are easy to understand, reuse, and maintain. The hierarchical approach enhances the scalability and flexibility of the design, allowing for efficient system development.

Keep in mind that module instantiation is just one aspect of designing with Verilog. In the upcoming section, we will explore the use of parameters and generics in Verilog modules, which enable us to create more flexible and configurable designs.

Parameters and Generics in Verilog Modules

In Verilog, module parameters and generics provide a powerful mechanism for creating flexible and configurable modules. By utilizing parameters and generics, Verilog designers can easily customize the behavior and functionality of their modules without modifying the underlying code. This section will explore the concept of parameters in Verilog modules and how they can be used to create generic and configurable modules.

Module Parameters

Verilog module parameters enable designers to define configurable values that can be specified during module instantiation. These parameters act as placeholders for values that can be set by the user, allowing for module customization without modifying the actual Verilog code. Module parameters are declared within the module definition and can be assigned default values.

Using module parameters, designers can create modules that are easily adaptable to different use cases. For example, a module parameter can be used to define the size of an array within the module. By changing the parameter value, the array size can be adjusted without modifying the module logic, making the module more versatile and reusable.

Here is an example of a Verilog module that utilizes parameters:

“`verilog

module MyModule

#(

parameter WIDTH = 8

)

(

input [WIDTH-1:0] data_in,

output [WIDTH-1:0] data_out

);

// Module logic goes here

endmodule

“`

Generic Modules

Verilog generics are similar to module parameters but provide a more flexible way of defining module characteristics. Generics are declared within the module definition and can be assigned values during module instantiation or overridden by the user.

Unlike module parameters, which are specified as part of the module instantiation, generics are defined as part of a template module that can be instantiated multiple times with different values assigned to the generics. This allows for the creation of generic modules that can be used in a wide range of scenarios.

Generics can be used to customize various aspects of a module, such as data widths, operation modes, or behavioral characteristics. For example, a generic module can be instantiated with different bit widths to handle different precision requirements, offering scalability and flexibility in design.

Here is an example of a generic module instantiation:

“`verilog

module MyGenericModule

#(

parameter WIDTH = 8

)

(

input [WIDTH-1:0] data_in,

output [WIDTH-1:0] data_out

);

// Module logic goes here

endmodule

module MyDesign;

// Instantiate MyGenericModule with different generic values

MyGenericModule #(4) inst1 (

.data_in(data_in),

.data_out(data_out)

);

MyGenericModule #(8) inst2 (

.data_in(data_in),

.data_out(data_out)

);

endmodule

“`

As shown in the example above, the same generic module, “MyGenericModule,” is instantiated twice with different values assigned to the WIDTH generic. This demonstrates the versatility and configurability achieved by utilizing generics in Verilog modules.

In conclusion, the use of parameters and generics in Verilog modules enhances flexibility and configurability, allowing for the creation of modules that can adapt to varying requirements without modifying the underlying code. By leveraging these features, Verilog designers can develop generic and configurable modules that provide efficiency and reusability in their designs.

Conclusion

In conclusion, understanding the module definition in Verilog is crucial for successful Verilog programming. Throughout this article, we have provided an overview of module definition, module structure, designing modules, instantiating modules, and using parameters and generics. By following the guidelines and best practices discussed, you can efficiently design and implement Verilog modules in your projects.

The module definition is the foundation of a Verilog design, providing a structured approach to organizing and connecting various components within a module. This allows for modularity, reusability, and scalability in Verilog programming.

In addition, the proper design of Verilog modules, including the use of hierarchical modules and reusable modules, can greatly enhance the efficiency and flexibility of your designs. By leveraging parameters and generics, you can create configurable modules that can be easily adapted to different requirements.

Overall, mastering the art of module definition in Verilog empowers you to create robust and efficient digital designs. By applying the principles and techniques discussed in this article, you can take your Verilog programming skills to the next level and develop high-quality designs that meet the demands of modern electronic systems.