Welcome to our comprehensive guide on packages and libraries in System Verilog. In this article, we will explore the importance of these fundamental components and how they contribute to efficient coding practices. Whether you are an experienced developer or new to System Verilog, understanding packages and libraries is essential for organizing your code, promoting modularity, and facilitating code reuse.

System Verilog, a hardware description and verification language, offers powerful features that enable developers to create complex digital designs. Packages and libraries are integral to this process, providing a structured approach to organizing code and promoting reusability.

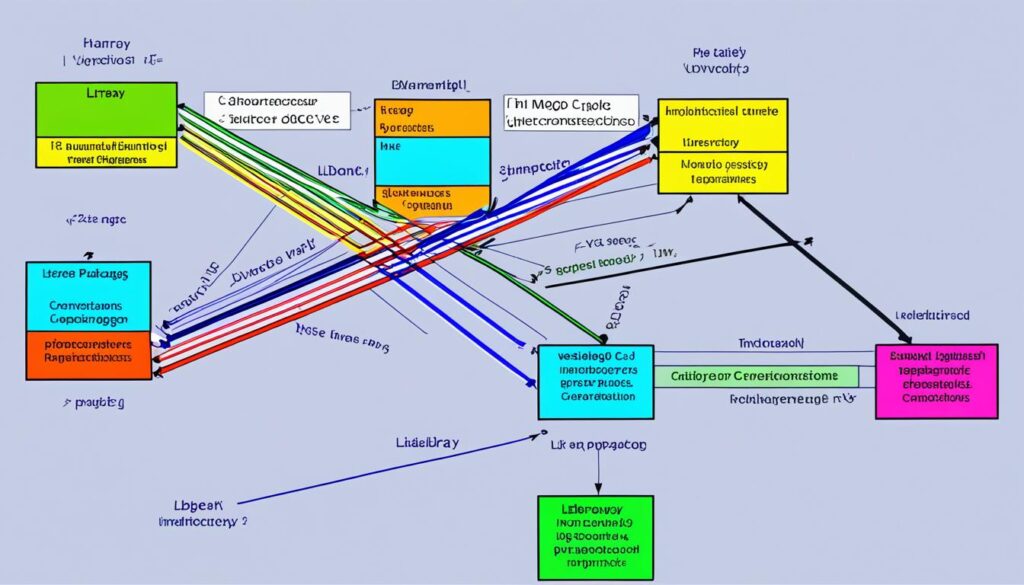

In the following sections, we will delve into the intricacies of packages and libraries in System Verilog. We will start by examining packages and their role in grouping related code elements together. Then, we will explore libraries and how they enable the sharing and reuse of code across multiple design projects. Finally, we will discuss the practical benefits of leveraging packages and libraries for efficient coding.

Throughout this article, we will provide insights and practical examples to help you grasp the concepts easily. So, let’s dive in and unravel the power of packages and libraries in System Verilog!

Table of Contents

Understanding Packages in System Verilog

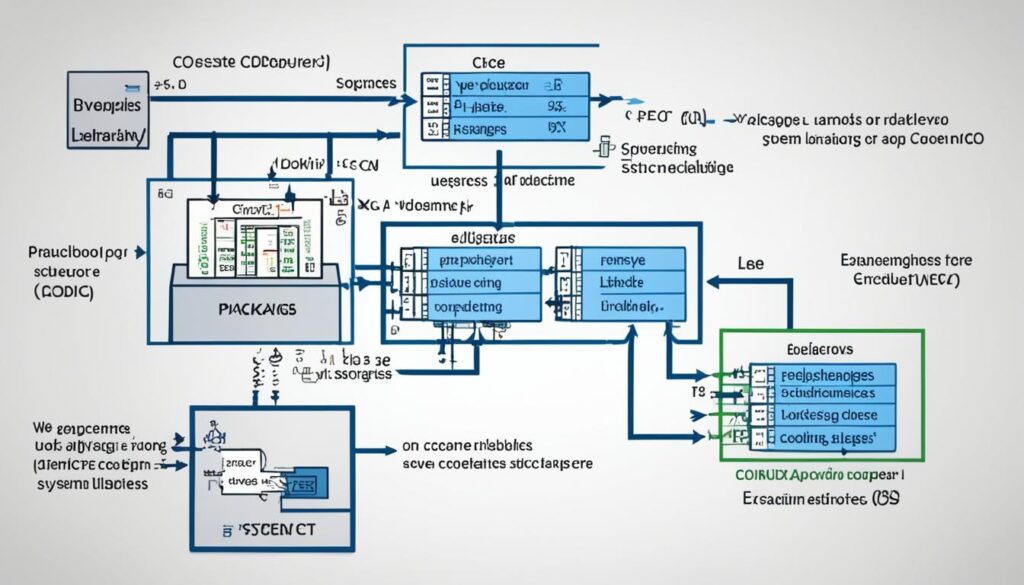

In System Verilog, packages are an essential component for organizing and structuring code. They allow us to group related code elements together, ensuring improved modularity and reusability.

So, what exactly are packages? In simple terms, a package is a container that holds a collection of declarations, definitions, and subroutines. The purpose of packages is to provide a convenient way to organize code elements, making it easier to manage complex designs. By encapsulating related code within a package, developers can create a logical structure that promotes efficient coding practices.

Packages in System Verilog offer several advantages. Firstly, they enhance modularity by allowing code to be divided into smaller, manageable units. This makes it easier to understand and maintain the code, as well as facilitate collaboration among team members. Additionally, packages enable code reuse by providing a mechanism for sharing functions, tasks, and variable declarations across different design projects. This not only saves development time but also ensures consistency and reliability in design implementation.

To better illustrate the concept of packages, let’s take a look at an example. Suppose we are working on a complex design project that involves multiple modules, each with its own set of functions and variables. Without packages, the code for each module might become cluttered and difficult to navigate. However, by organizing the code elements related to each module into separate packages, we can create a clear structure that promotes maintainability and reusability.

Here is an example of how packages can be used in System Verilog:

package Arithmetic;

function int add(int a, int b);

return a + b;

endfunction

function int subtract(int a, int b);

return a - b;

endfunction

endpackage

package Logic;

function int and_gate(int a, int b);

return a & b;

endfunction

function int or_gate(int a, int b);

return a | b;

endfunction

endpackage

In the example above, we have defined two packages: “Arithmetic” and “Logic”. Each package contains separate functions relevant to arithmetic and logic operations, respectively. By grouping related functions within packages, we establish a modular and reusable code structure.

Understanding how packages work in System Verilog is crucial for efficient coding and design. By leveraging packages, developers can enhance code organization, promote modularity, and facilitate code reuse. Now that we have a clear understanding of packages, let’s explore the role of libraries in System Verilog in the next section.

Exploring Libraries in System Verilog

In System Verilog, libraries play a vital role in organizing and managing code. They are repositories for code modules that allow developers to effectively share and reuse their work across different design projects.

A library in System Verilog is a collection of related code modules organized into separate logical units. It provides a structured environment for code organization, allowing developers to compartmentalize their designs and easily locate the necessary modules for a specific task.

Leveraging libraries enables efficient code reuse, as developers can easily access and incorporate previously written code modules into new projects. This saves valuable development time and promotes consistency and standardization across designs.

Creating and Managing Libraries

To create a library in System Verilog, developers need to follow a few simple steps:

- Create a new directory on the file system to serve as the library’s root directory.

- Define a library name, which will be associated with the root directory.

- Store code modules within subdirectories based on their functionality or purpose within the library.

To ensure effective library management, developers can use tools such as the QuestaSim simulator or the ModelSim software. These tools provide graphical user interfaces that simplify the creation and organization of libraries.

Library Usage and Benefits

Libraries in System Verilog offer several key benefits:

- Modularity: Libraries allow developers to break down their code into modular components, making it easier to understand, maintain, and update.

- Code Reuse: By storing commonly used code modules in libraries, developers can effortlessly reuse them in different projects, boosting productivity and efficiency.

- Collaboration: Libraries facilitate collaboration among team members by centralizing code resources and enabling seamless sharing and integration of modules.

- Code Organization: Libraries provide a systematic approach to organizing code, allowing developers to locate and manage code modules quickly and efficiently.

The proper utilization of libraries in System Verilog can significantly enhance the development process, promote code reuse, and streamline project management.

| Library | Description |

|---|---|

| lib1 | A library containing commonly used functions and utilities. |

| lib2 | A library specific to a particular design project, containing modules specific to that project’s requirements. |

| lib3 | A library for experimental modules and testbenches, separate from the main design libraries. |

Leveraging Packages and Libraries for Efficient Coding

In the world of System Verilog, efficient coding is paramount to successful design implementation. By leveraging packages and libraries, developers can significantly enhance their coding practices, leading to improved modularity, code reuse, and overall coding efficiency.

Code Modularity

Packages and libraries serve as indispensable tools for enhancing code modularity in System Verilog. A package is a container that encapsulates related code elements such as data types, parameters, and functions. It allows developers to organize their code into logical units, making it easier to understand, maintain, and reuse. With packages, developers can encapsulate commonly used functions or design components, promoting code reusability across multiple projects. This modular approach streamlines code development and debugging processes, ultimately saving valuable time and effort.

Promoting Code Reuse

One of the key advantages of using packages and libraries in System Verilog is the ability to promote code reuse. When developers create a package, they can define and share code that can be easily imported and utilized in other design projects. This not only saves time by eliminating the need to rewrite code from scratch but also ensures consistency and improves reliability. By leveraging existing code through libraries, developers can build upon the work of others and accelerate the development process.

Enhancing Overall Coding Efficiency

Efficient coding is all about reducing redundancy and improving productivity. By harnessing the power of packages and libraries, developers can achieve this goal. Packages and libraries allow for the creation of a collective library of commonly used code, making it readily accessible for future projects. This eliminates the need to reinvent the wheel, maximizes code reuse, and reduces the chances of errors. With well-documented packages and extensively tested libraries, developers can focus on solving unique design challenges rather than dwelling on repetitive coding tasks.

| Benefits of Packages and Libraries for Efficient Coding | Explanation |

|---|---|

| Improved Modularity | Packages allow grouping of related code elements, enhancing organization and maintainability. |

| Code Reusability | Packages and libraries enable sharing and reusing code across different design projects, saving time and effort. |

| Reduced Redundancy | Using existing code through libraries eliminates the need to rewrite code and promotes productivity. |

| Error Minimization | Well-documented packages and extensively tested libraries improve code reliability and reduce the chances of errors. |

Conclusion

In conclusion, we have explored the pivotal role that packages and libraries play in System Verilog. Packages and libraries are essential tools for efficient coding, as they have the ability to organize code, promote modularity, and encourage reuse. By harnessing the power of packages and libraries, developers can streamline their coding process and create more robust and maintainable designs.

Packages in System Verilog allow code elements to be grouped together for improved modularity and reusability. They provide a structured approach to organizing code, making it easier to manage and navigate complex designs. Libraries, on the other hand, enable the sharing and reuse of code across different design projects. This promotes code reuse, saving valuable development time and effort.

By utilizing packages and libraries, developers can enhance their coding efficiency. They can leverage existing code modules stored in packages and libraries, avoiding the need to rewrite code from scratch. This not only saves time but also reduces the chances of introducing errors. Packages and libraries also encourage consistent coding practices, as they provide a standardized framework for code organization.

In summary, packages and libraries are indispensable tools in System Verilog. They empower developers to build scalable, modular, and reusable designs. By adopting a systematic approach to code organization and reusability, developers can optimize their coding process and develop high-quality designs. The strategic use of packages and libraries is key to creating efficient and maintainable designs in System Verilog.