The semiconductor industry has undergone a significant transformation with the advent of FinFET technology, which has become the dominant gate design at advanced process nodes like 14 nm, 10 nm, and 7 nm. This transition from planar CMOS to FinFET architecture has profoundly impacted the way we approach physical design in integrated circuits. FinFET transistors, with their unique vertical fin structure, offer enhanced performance and density, but they also introduce new challenges that require a deep understanding of the technology’s underlying principles.

FinFET technology has fundamentally changed the way we design and implement integrated circuits. The vertical fin structure, where multiple fins are arranged side by side and covered by a single gate, enables improved drive strength and performance. However, this new transistor architecture also presents significant design and manufacturing challenges, particularly in terms of multi-patterning lithography requirements and the impact on implementation tools.

As we navigate the complexities of FinFET design, we must adapt our physical design strategies to address the unique constraints and requirements of this technology. From device placement and density management to design rule compliance and proximity effects, the influence of FinFET technology on physical design is profound and far-reaching. In this article, we will explore the key principles of FinFET technology and delve into the critical aspects of physical design that must be considered to ensure successful implementation and first-time-right silicon.

Table of Contents

Understanding the Evolution of Physical Design in IC Manufacturing

The evolution of physical design in IC (integrated circuit) manufacturing has been marked by a significant shift from planar CMOS (complementary metal-oxide-semiconductor) technology to the emergence of FinFET (Fin field-effect transistor) architecture. This transition occurred in the early 2010s as the industry faced the physical limits of Moore’s Law and Dennard scaling, which had driven the relentless miniaturization of transistors for decades.

From Planar CMOS to Modern Solutions

As traditional planar CMOS designs approached the sub-20nm nodes, the industry recognized the need for a more innovative approach to maintain the performance and power efficiency improvements that had become the hallmark of semiconductor advancements. The shift to FinFET technology represented a significant departure from the planar structure, introducing a vertical, three-dimensional transistor design that offered better electrostatic control and reduced leakage currents.

The Shift to Sub-20nm Nodes

The move to smaller transistor nodes, particularly sub-20nm, required a fundamental rethinking of physical design strategies. Traditional MOSFET (metal-oxide-semiconductor field-effect transistor) designs suffered from increased leakage currents and power dissipation, which threatened to undermine the performance gains achieved through scaling. FinFET technology emerged as a viable solution, providing enhanced performance, higher drive currents, and reduced power consumption at these advanced nodes.

Challenges in Layout Complexity

The transition to FinFET technology has brought about a significant increase in layout complexity. As the number and intricacy of design rules have grown exponentially to accommodate the increasing density of transistors, engineers have had to develop new design strategies and tools to address the unique constraints of this advanced technology. Managing the three-dimensional nature of FinFETs, optimizing fin placement, and ensuring compliance with the evolving design rules have become critical considerations in physical design.

| Key Characteristics | Planar CMOS | FinFET Technology |

|---|---|---|

| Transistor Structure | Flat, two-dimensional | Vertical, three-dimensional |

| Electrostatic Control | Limited | Enhanced |

| Leakage Currents | Higher | Lower |

| Power Consumption | Higher | Lower |

| Performance | Limited | Improved |

| Layout Complexity | Relatively Simple | Significantly Increased |

The evolution of physical design in IC manufacturing has been a story of adaptation and innovation, driven by the ever-increasing demands for performance, power efficiency, and density. The shift from planar CMOS to FinFET technology has been a crucial step in this ongoing journey, paving the way for continued advancements in the semiconductor industry.

Core Principles of FinFET Technology

FinFET technology is revolutionizing the landscape of integrated circuit (IC) manufacturing, offering a unique approach to transistor design. At the heart of FinFETs lies the vertical fin structure, a distinct departure from traditional planar CMOS transistors. This innovative fin, made of doped silicon, serves as the channel where the transistor action takes place.

One of the key advantages of the FinFET design is the gate polysilicon’s ability to interface with the source and drain on multiple surfaces. This wrap-around gate structure enhances the control and performance of the device, providing better control of the channel, reduced leakage, and improved performance at lower voltages compared to planar transistors.

FinFETs can be constructed on either bulk silicon or silicon-on-insulator (SOI) substrates, offering flexibility in manufacturing processes. The channel is formed wherever the gate poly contacts the fin, resulting in improved electrical characteristics and a more robust device structure.

- The gate in FinFETs surrounds multiple sides of the channel, forming a multigate structure unlike planar MOSFETs.

- The fin structure in FinFETs provides more volume within the same surface area compared to planar transistors.

- FinFETs reduce sensitivity to dopant-induced variations due to their thin body and wrap-around gate structure.

As semiconductor technology continues to advance, FinFET architecture has played a crucial role in extending Moore’s Law, enabling a roadmap to further scaling in semiconductor chips. The unique design principles of FinFET technology have paved the way for continued advancements in IC performance, power efficiency, and device scaling.

Impact of Grid-Based Device Placement on Layout Design

In the realm of FinFET technology, grid-based device placement is a fundamental aspect of the layout design process. The fin grid pitch, typically around 30nm, and the poly grid pitch (contacted poly pitch) of about 50nm, dictate strict placement rules that designers must adhere to. Transistor widths are quantized based on the number of fin crossings, with each crossing adding approximately 10-100nm to the width.

Fin Grid Pitch Considerations

The fin grid pitch, which determines the spacing between adjacent fins, is a critical parameter in FinFET layout design. This pitch, typically around 30nm, must be precisely maintained to ensure optimal device performance and yield. Designers must carefully plan the placement of fins to align with this grid, maximizing the utilization of available space while meeting the necessary design rules.

Gate Length Restrictions

Another significant constraint in FinFET layout design is the limited options for gate lengths. Gate lengths are severely restricted, usually limited to two or three options for different voltage requirements. This limitation is a result of the advanced manufacturing processes employed in FinFET technology, where precise control over the gate dimensions is essential for achieving the desired device characteristics.

Placement Constraints in Advanced Nodes

As the semiconductor industry progresses to more advanced nodes, the layout design challenges become increasingly complex. The grid-based nature of FinFET design necessitates careful planning and consideration of placement constraints throughout the layout process. Designers must ensure that the placement of devices, interconnects, and other layout elements adheres to the strict grid rules to optimize device performance, power, and yield.

The impact of grid-based device placement on FinFET layout design is significant, as it shapes the overall structure and characteristics of the final layout. By understanding and effectively managing these constraints, designers can create highly uniform and optimized layouts that unlock the full potential of FinFET technology in advanced semiconductor applications.

Density Management and Gradient Control in FinFET Designs

As the semiconductor industry continues to push the boundaries of transistor scaling, density management and gradient control have become critical aspects of FinFET design. Strict requirements for minimum density, maximum density, and density gradients must be carefully considered during the floor planning stage. These rules are particularly crucial for polygate structures, as shape density and density gradients can significantly impact layout-induced variability.

Automated fill algorithms are often employed to meet these density-related ground rules, but in complex cases, manual intervention may be necessary. Density gradient constraints are especially important when placing blocks with different gate lengths adjacently, potentially requiring transition regions or special fill shapes to maintain the desired density profile. Metal layers also have density limits, necessitating careful planning and potentially simulated fill algorithms during the layout design rule check (DRC) process.

| Key Considerations for Density Management in FinFET Designs | Impact |

|---|---|

| Minimum Density Requirements | Ensure consistent electrical performance and prevent layout-induced variability |

| Maximum Density Restrictions | Mitigate issues related to thermal, mechanical, and chemical-mechanical polishing (CMP) effects |

| Density Gradient Control | Maintain uniform electrical characteristics across the chip, particularly important for adjacent blocks with different gate lengths |

| Automated Fill Algorithms | Assist in meeting density requirements, but may require manual intervention in complex cases |

By addressing these density management and gradient control challenges, designers can ensure the successful implementation of FinFET technology, optimizing device performance and reliability while navigating the complexities of advanced semiconductor manufacturing.

Layout Planning Strategies for FinFET Implementation

Effective layout planning is crucial for successful FinFET implementation. As we migrate to advanced nodes, the complexity of layout design continues to escalate, requiring meticulous strategies to address the unique challenges posed by FinFET technology.

Block Placement Optimization

Block placement must be optimized to adhere to the strict grid constraints and density requirements of FinFET designs. We need to carefully consider the fin grid pitch, gate length restrictions, and other placement constraints to ensure efficient utilization of the available area.

Termination Structure Requirements

All blocks, from small op-amps to large IP blocks, require termination or “finishing” structures around their periphery. These structures can significantly impact the overall area usage, making early planning critical to avoid time-consuming rework.

Power Distribution Considerations

Power distribution is a key consideration in FinFET layouts. Substrate and N-well biasing require careful planning, as the area required for boundary and tap structures can be substantial. Implementing these strategies early in the design process is vital for creating efficient and manufacturable FinFET layouts.

| Parameter | 28nm Planar | 16nm FinFET |

|---|---|---|

| Cost per Transistor | $0.10 | $0.15 |

| Power Efficiency | Moderate | High |

| Maximum Frequency | 2 GHz | 3 GHz |

As we can see, the transition to FinFET technology brings both challenges and opportunities. By implementing effective layout planning strategies, we can unlock the full potential of FinFET designs and deliver high-performance, power-efficient integrated circuits.

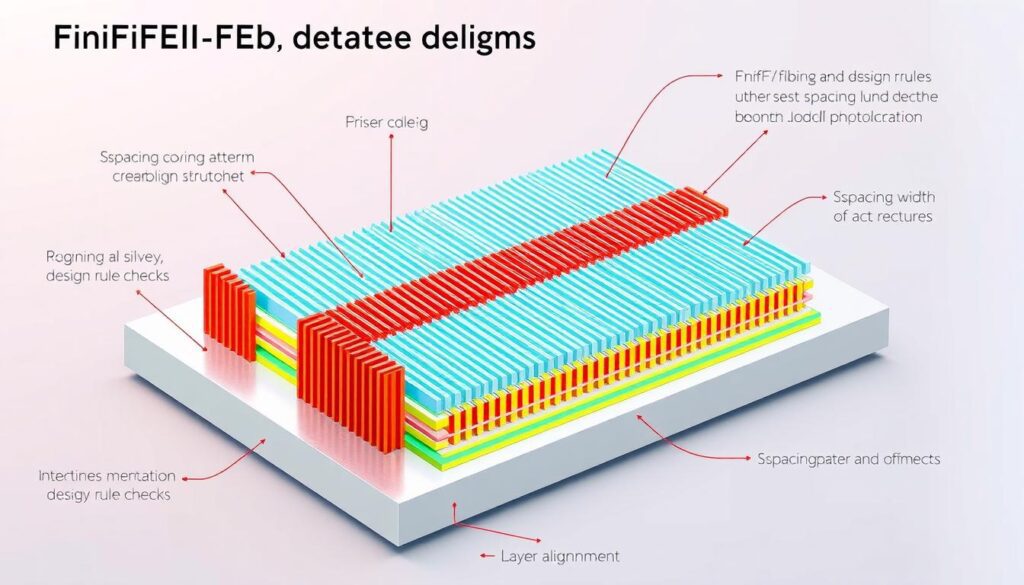

Critical Design Rule Checks for FinFET Layouts

Designing FinFET layouts requires meticulous attention to detail, as the complex 3D structure and advanced manufacturing processes introduce a multitude of design rules that must be thoroughly checked. Design Rule Checking (DRC) is a critical step in the FinFET layout design flow, ensuring compliance with a vast array of termination, continuous diffusion, density, and cut shape placement requirements.

One of the key considerations is performing front-end DRC before any metal routing. This early verification helps avoid difficult and time-consuming rework later in the design process. Cut shapes for poly and diffusion contact breaks must be carefully placed, adhering to specific design rules while potentially offering some flexibility for optimizing parasitics or density.

To further ensure DRC compliance, very low-level cells, such as standard logic gates, should be tested in situ using prepared testbench layouts. This comprehensive approach helps identify and resolve any design rule violations early on, streamlining the overall FinFET layout implementation.

| Design Rule Checks | Importance |

|---|---|

| Termination Rules | Ensure proper device termination and isolation, critical for FinFET performance and reliability |

| Continuous Diffusion Rules | Enforce continuous diffusion for optimal transistor matching and leakage control |

| Density Rules | Maintain consistent density across the layout to mitigate issues like chemical-mechanical polishing (CMP) variations |

| Cut Shape Placement | Properly position contact cut shapes to optimize parasitics and layout density |

By rigorously applying these critical design rule checks, FinFET layout designers can ensure their designs are compliant, manufacturable, and optimized for performance, power, and reliability.

Managing Proximity Effects and Continuous Diffusion

In the realm of FinFET technology, managing proximity effects and continuous diffusion is a critical aspect of layout design. The proximity of active gates to diffusion edges can significantly impact device performance due to crystal lattice stress, a phenomenon known as edge proximity impact. To mitigate these effects, FinFET designs often employ continuous diffusion practices, leveraging dummy devices in electrically off states to maintain consistent spacing throughout the layout.

Edge Proximity Impact

The distance between active gates and diffusion edges plays a crucial role in FinFET performance. As the technology scales to smaller nodes, this edge proximity can lead to significant variations in device characteristics, such as threshold voltage and drive current. Careful management of edge proximity is essential to ensure consistent and reliable device behavior across the chip.

Dummy Device Placement

To address the challenges posed by edge proximity, FinFET designers often utilize continuous diffusion techniques. This approach involves the placement of dummy devices in electrically off states, strategically positioned to maintain uniform spacing between active devices. By maintaining a consistent row-based layout, where all devices in a given row have the same number of fins, the impact of edge proximity can be effectively managed.

Well Edge Considerations

While the impact of N-well edge proximity is less significant in FinFET layouts compared to planar CMOS, it is still an important factor to consider. The continuous diffusion practices employed in FinFET designs help maintain consistent device performance and reduce variability across the chip, including the management of N-well edge effects.

By mastering the techniques of managing proximity effects and continuous diffusion, FinFET designers can ensure the optimal performance, reliability, and scalability of their advanced semiconductor devices.

Advanced Manufacturing Requirements for FinFET Designs

As the semiconductor industry rapidly advances towards smaller process nodes, the design and manufacturing of FinFET-based integrated circuits have become increasingly complex. To enable the production of high-performance, power-efficient FinFET chips, we must employ sophisticated manufacturing techniques and design tools that can handle the unique challenges presented by these advanced transistor structures.

One of the primary concerns is the need for multi-patterning lithography, which is essential for patterning the intricate features of FinFET devices. This, in turn, requires rule-aware placement and routing algorithms to ensure efficient mask coloring and minimize manufacturing complexity. Additionally, in-design physical verification throughout the design flow is crucial to reduce iterations and address any potential manufacturing issues early on.

Accurate extraction and timing analysis are also vital to account for the increased manufacturing variability associated with FinFET technology. Our design tools must be capable of handling multi-GHz+ operating frequencies, necessitating improved modeling, guidance, and analysis capabilities. Synopsys offers a comprehensive, foundry-certified solution suite that addresses these advanced requirements, enabling the successful implementation and volume production of FinFET designs in modern semiconductor manufacturing.

Source Links

- What is a FinFET? – Benefits & How it Works | Synopsys

- FinFET Technology and Layout – Part 1 | ASIC North

- Understanding FinFET Technology: A Comprehensive Overview

- Comprehensive Review of FinFET Technology: History, Structure, Challenges, Innovations, and Emerging Sensing Applications

- The Basics of FinFET Technology

- Tech Brief: FinFET Fundamentals

- US20170061056A1 – Cell grid architecture for finfet technology

- ARM tools take aim at finFET layout, timing issues

- Tackling Layout Gradient Effects in 16 nm FinFET using Layout Automation – Semiwiki

- High-voltage FinFET with floating poly and high-k material for enhanced intrinsic gain and safe operating area – Scientific Reports

- finFET tipsheet for IEDM – Tech Design Forum

- Finfet Layout Guidelines – for Beginners and Professionals

- Lessons learned in the finFET trenches

- Designing an SoC with 16nm FinFET – Semiwiki

- FinFET Back-End Layout, Analog Techniques, and Design Tools

- FinFET Design | DesignWare IP | Synopsys

- US10580867B1 – FINFET including source and drain regions with dopant diffusion blocking superlattice layers to reduce contact resistance

- 4B-3 Multi-Cell Soft Errors at the 16-nm FinFET Technology Node

- FinFET Transistors: The Technology Behind Advanced Processors

- A Review Paper on CMOS, SOI and FinFET Technology