Welcome to our article on the basics of clock domain crossing (CDC). In this digital design-focused discussion, we will delve into the intricacies of clock domain verification and the challenges associated with transferring data across different clock domains. Clock domain crossing plays a vital role in the design of complex systems-on-chip (SoCs), where functionality is spread across multiple domains.

Traditional verification methods such as simulation and static timing analysis are insufficient when it comes to ensuring the consistent and reliable transfer of data across clock domains. This is where new verification methodologies come into play, helping address issues like metastability, data loss, and data incoherency.

To gain a comprehensive understanding of clock domain crossing and its importance in digital design, join us as we explore the different issues and solutions related to CDC, the techniques employed to handle clock domain crossing, and some essential tips for designing clock domain crossing circuits.

Table of Contents

Clock Domain Crossing Issues and Solutions

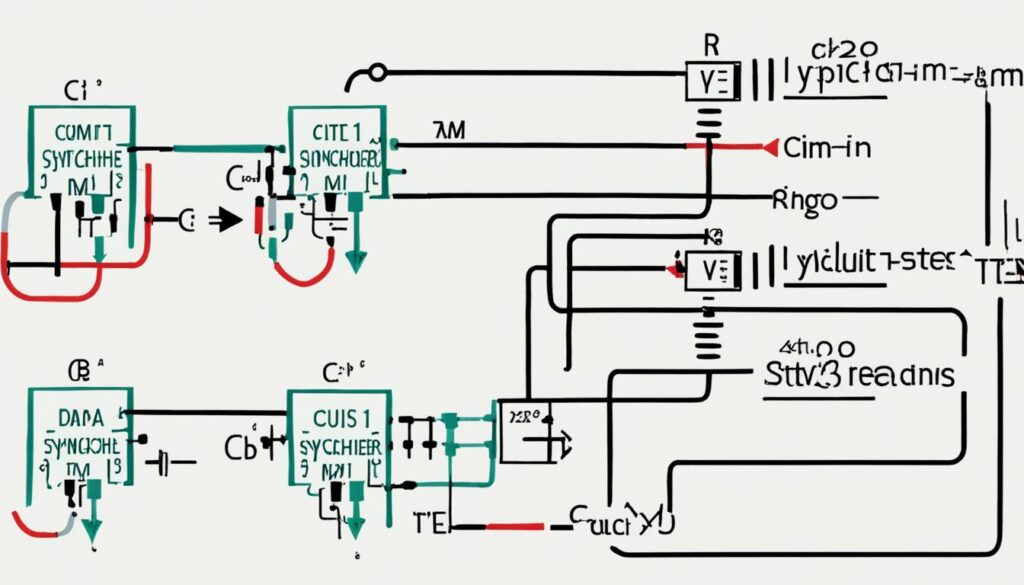

Clock domain crossing poses various challenges that must be addressed to ensure the smooth transfer of data. One significant issue is metastability, which occurs when there is a signal transition near the active edge of the destination clock. This situation can lead to setup or hold violations, resulting in an unstable output in the destination domain for an indefinite period. To tackle metastability, synchronizers are employed. A widely used synchronizer is the two-flip-flop synchronizer, which allows ample time for oscillations to settle and ensures a stable output in the destination domain.

Another issue is data loss, which arises when the destination domain fails to capture new source data during the first cycle of the destination clock. Techniques such as handshake protocols and First-In-First-Out (FIFO) architectures can be implemented to guarantee the complete capture of each source data transition in the destination domain.

Data incoherency is yet another concern inherent in clock domain crossing, especially when transferring multiple signals across domains. This issue can be resolved by synchronizing the signals using techniques such as Gray code encoding or handshake protocols, ensuring consistency and coherence in the transferred data.

Common Clock Domain Crossing Issues:

- Metastability: Signal transitions near the active edge of the destination clock

- Data Loss: Failure to capture new source data during the first cycle

- Data Incoherency: Inconsistent and incoherent transfer of multiple signals

To address these clock domain crossing concerns, it is crucial to utilize appropriate synchronization techniques and design methodologies. By implementing effective solutions, designers can mitigate the risks associated with metastability, data loss, and data incoherency. This ensures the reliable and synchronized transfer of data across clock domains, leading to improved system performance and functionality.

Clock Domain Crossing Techniques

Various techniques can be employed to handle clock domain crossing in digital designs. One commonly used technique is the usage of synchronizer circuits, which help protect against metastability issues. A dual flip-flop synchronizer, consisting of two flip-flops connected in series in the destination clock domain, is an effective solution for many applications involving single-bit control signals.

For applications where the source and destination clock frequencies are almost the same, or the destination clock frequency is slower, the handshake technique can be employed. In this technique, the source domain sends a request signal to the destination domain, which responds with an ack signal indicating successful reception.

For applications with higher bandwidth requirements, a dual clock asynchronous FIFO can be used to transfer data between clock domains. This FIFO ensures data integrity by providing buffering and synchronization mechanisms.

Clock gating can also result in multiple clock domains, where the slower domain changes from one second to the next. Clock gating techniques are used to conserve power by enabling or disabling clocks to specific portions of the circuit, resulting in multiple clock domains within the design.

Comparison between Clock Domain Crossing Techniques

| Technique | Advantages | Disadvantages |

|---|---|---|

| Synchronizer circuits | – Protect against metastability issues – Efficient for single-bit control signals |

– Limited scalability for larger data transfers |

| Handshake technique | – Ensures synchronized data transfer – Well-suited for similar or slower clock frequencies |

– Additional overhead in signaling |

| Asynchronous FIFO | – Supports higher bandwidth data transfers – Provides buffering and synchronization mechanisms |

– Larger area and complexity |

| Clock gating | – Power-saving mechanism – Enables multiple clock domains |

– Requires careful design and verification |

When deciding on the appropriate clock domain crossing technique for a specific design, it is crucial to consider factors such as the signal characteristics, data transfer requirements, power constraints, and performance goals. By leveraging these techniques effectively, designers can ensure smooth and reliable data transfer between clock domains in their digital designs.

Clock Domain Crossing Tips

Designing clock domain crossing (CDC) circuits requires careful consideration and implementation of best practices to ensure reliable data transfer. By following proper CDC design techniques, synchronizer placement, and avoiding synchronization duplication, designers can minimize debug challenges and optimize the performance of their designs.

CDC Design Techniques

When it comes to CDC design, employing the right techniques can make a significant difference in the overall reliability of the system. Some essential CDC design techniques include:

- Eliminating Combinatorial Paths: It is crucial to eliminate combinatorial paths between clock domains to prevent issues like data loss and metastability. By minimizing the number of combinational logic elements between different clock domains, designers can enhance the overall stability and performance of the design.

- Synchronizer Placement: Proper placement of flip-flops forming synchronizer circuits is essential to minimize clock skew and ensure reliable data transfer. Placing flip-flops close to each other reduces the synchronization delay and improves the synchronization process.

- Avoiding Synchronization Duplication: Synchronizing the same signal in multiple places can lead to synchronization duplication, which may result in design issues and potential data inconsistencies. It is crucial to carefully analyze the synchronization requirements and avoid unnecessary duplication.

Debug Challenges

Clock domain crossing introduces unique challenges during the debug phase. Identifying and resolving CDC-related issues can be time-consuming and complex. Some common debug challenges associated with clock domain crossing include:

- Metastability: Dealing with metastability issues and their impact on the system’s behavior can be challenging. Proper testing and verification techniques are necessary to identify and mitigate metastability-related problems.

- Data Loss: Ensuring that the destination domain captures all transitions from the source domain is crucial to prevent data loss. Debugging data loss issues requires careful inspection of the synchronization process and verification of signal integrity.

- Clock Skew: Clock skew between different clock domains can affect the reliable transfer of data. Debugging clock skew-related problems requires analyzing clock distribution and ensuring consistent clock edges.

Conclusion

In conclusion, clock domain crossing is a critical aspect of digital design, particularly in complex systems-on-chip (SoCs). The successful transfer of data between different clock domains requires careful consideration of issues such as metastability, data loss, and data incoherency. By employing proper clock domain crossing techniques, such as synchronizers, dual flip-flop synchronizers, handshake protocols, FIFOs, and clock gating mechanisms, designers can ensure reliable and efficient data transfer across clock domains.

Investing time in understanding and implementing good clock domain crossing design practices can significantly enhance the overall quality and performance of digital designs in modern SoCs. It is crucial for designers to address clock domain crossing challenges early in the design phase, using appropriate verification methodologies to validate the reliability of data transfer. Traditional verification methods like simulation and static timing analysis are often insufficient and new approaches are required to ensure consistent and reliable data transfer.

By applying these clock domain crossing techniques and verification methodologies, designers can minimize the risks associated with clock domain crossing, avoid issues like metastability and data loss, and ensure the coherency of data across clock domains. Ultimately, this leads to improved functionality, performance, and reliability of digital designs in SoCs, enabling the successful deployment of cutting-edge technologies in various industries.