In the world of PCB design, it’s key to fight crosstalk and parasitics, more so in high-speed circuits. These issues can cause signal interference and lower performance. As a professional copywriter, I’ll show you how to reduce these problems and keep your PCB layouts working well.

This article will cover the basics and practical tips for keeping signals clean in your designs. We’ll look at trace routing, choosing the right components, and using ground planes. By learning about crosstalk and parasitics, and how to lay out your PCB, you can make high-speed circuits that work reliably and efficiently.

Table of Contents

Understanding Crosstalk and Parasitics Fundamentals

Good circuit design needs a solid grasp of crosstalk and parasitic effects. Crosstalk happens when unwanted electromagnetic fields link PCB traces. This includes both inductive (magnetic) and capacitive (electric) coupling. Inductive coupling makes voltage in nearby traces through magnetic fields. Capacitive coupling, on the other hand, creates unwanted capacitance.

These issues can cause signal loss, noise, and errors in logic states. This greatly affects how well a circuit works.

Electromagnetic Coupling Basics

Electromagnetic coupling is key to signal quality. Near-field electric field coupling is called capacitive, while near-field magnetic field coupling is inductive. Far-field coupling is about electromagnetic fields.

Types of Signal Interference

Crosstalk shows up in different ways, like conducted and radiated coupling. Capacitive coupling happens when two conductors with a voltage difference are separated by a dielectric. The parasitic capacitance changes with frequency, impacting circuit performance.

Impact on Circuit Performance

The amount of noise voltage and mutual inductance depends on current switching rate and magnetic field strength. Designers must figure out the maximum voltage shared between circuits to set crosstalk limits. To fight crosstalk, designers use spacing, shorten parallel runs, and terminate signals wisely.

| Crosstalk Mitigation Strategies | Impact |

|---|---|

| Increased Spacing Between Traces | Reduces capacitive and inductive coupling, decreasing crosstalk magnitude |

| Shorter Parallel Run Lengths | Limits the area over which coupling can occur, reducing crosstalk |

| Effective Signal Termination | Can help improve crosstalk behavior in certain scenarios when applied correctly |

| Proximity to Reference Planes | Decreasing distance to reference planes can reduce crosstalk by providing a low-impedance return path |

PCB Layout Best Practices for Signal Integrity

Keeping signal integrity is key in PCB design, more so in high-speed circuits. By sticking to some layout best practices, engineers can fight off crosstalk and parasitic elements. These methods include:

- Maintaining sufficient trace spacing: Keeping at least three times the trace width between adjacent signals can help minimize electromagnetic coupling and crosstalk.

- Utilizing perpendicular routing: Placing traces on adjacent layers in a perpendicular orientation can reduce the mutual inductance and capacitance between them, improving signal integrity.

- Implementing ground planes: Continuous ground planes between signal layers act as a shield, preventing electromagnetic interference and providing a low-impedance return path for signals.

- Employing differential signaling: Using complementary signal pairs with opposite polarity can help cancel out common-mode noise and improve signal-to-noise ratio.

It’s also important to keep high-frequency and asynchronous signals away from other traces. This helps prevent crosstalk and keeps signal integrity in PCB designs. By using these layout best practices, engineers can make sure circuits work well and reliably.

| Technique | Description | Benefit |

|---|---|---|

| Trace Spacing | Maintaining at least three times the trace width between adjacent signals | Minimizes electromagnetic coupling and crosstalk |

| Perpendicular Routing | Placing traces on adjacent layers in a perpendicular orientation | Reduces mutual inductance and capacitance between traces |

| Ground Planes | Implementing continuous ground planes between signal layers | Provides a low-impedance return path and shields against EMI |

| Differential Signaling | Using complementary signal pairs with opposite polarity | Cancels out common-mode noise and improves signal-to-noise ratio |

Managing Crosstalk and Parasitics in High-Speed Designs

As we need faster processing and higher bandwidth, high-frequency circuit design is key in embedded engineering. In these fast environments, parasitic effects like signal loss and interference can harm circuit performance. These effects can change impedance, reduce signal quality, cause power loss, and affect timing in digital circuits.

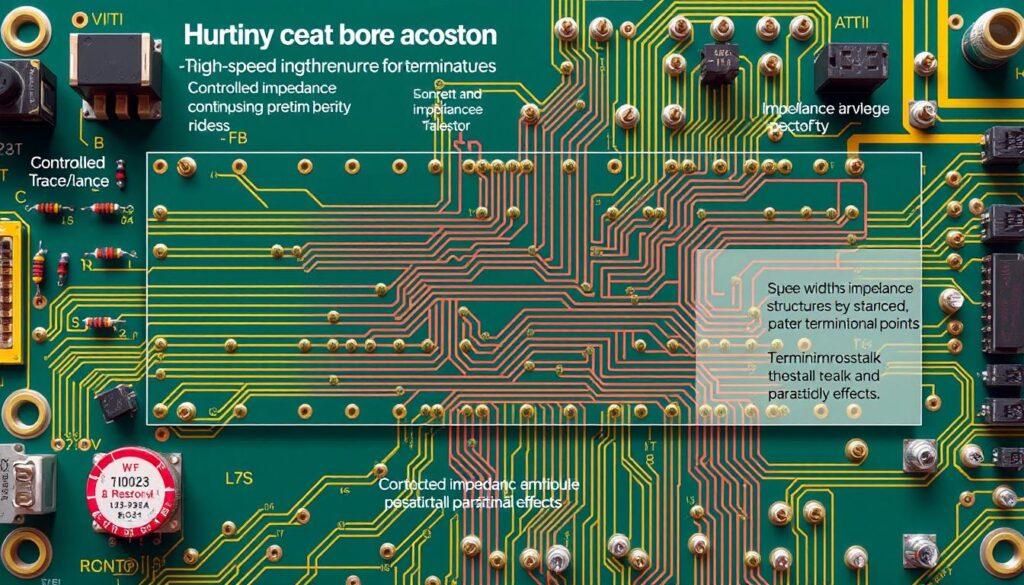

Trace Width and Spacing Guidelines

Keeping impedance under control is vital for high-speed designs. Using microstrip or stripline and calculating trace widths correctly is essential. Short traces and fewer vias help fight parasitic effects.

Ground Plane Implementation

Ground planes are crucial for a low-inductance return path for signals. By closely linking the signal return path to the ground plane, you can lessen parasitic inductance and capacitance.

Return Path Optimization

Optimizing the signal return path is key for managing crosstalk and parasitics. Make sure the return path is close to the signal traces to reduce electromagnetic coupling. Tools like Cadence Allegro’s Crosstalk Analysis Tool help spot and fix crosstalk issues.

By following these best practices, you can manage crosstalk and parasitics in high-speed designs. This ensures signal integrity and overall system performance.

Advanced Routing Techniques for EMI Reduction

Electromagnetic interference (EMI) is a big challenge in high-speed circuit designs. Advanced routing techniques are key to solving this problem. Guard traces with grounded vias act as protective barriers to contain and reduce EMI.

By placing these grounded traces next to sensitive signal traces, I can shield against unwanted electromagnetic coupling. This prevents interference from spreading through the circuit.

Grounding strategies are also crucial in reducing EMI. It’s important to have a continuous and unbroken ground reference plane. This avoids ground loops, which can act as antennas and emit unwanted electromagnetic radiation.

Stitching vias between the top and bottom ground planes also helps. It reduces loop inductance, making the circuit more immune to EMI.

When external connections are needed, shielded cables are recommended. These cables have conductive outer shields that block electromagnetic interference. They prevent it from entering or leaving the circuit.

By using these advanced routing techniques, I can minimize EMI. This ensures high-speed signals are reliable and meet regulatory standards.

Source Links

- The best crosstalk reduction techniques

- How To Eliminate Crosstalk In Your High-speed PCB Design

- Handling Crosstalk in High-Speed PCB Design | Sierra Circuits

- Crosstalk Basics in PCB Design

- Exploring the Characteristics of Field Coupled Crosstalk – In Compliance Magazine

- Signal Integrity Design Considerations for High Speed Design

- Enhancing Signal Integrity in PCB Design: Key Considerations and Strategies

- Our PCB design hints for improving signal integrity

- How to Minimize Parasitic Effects in High-Frequency Circuit Design – RunTime Recruitment

- How To Remove Parasitic Capacitance in High-Speed Designs

- How to Reduce EMI to Improve Signal Integrity | Sierra Circuits

- Techniques to Reduce EMI In Your PCB Designs

- Routing High Speed Signals: Best Practices | EMA Design Automation