Welcome to our article on worst-case timing analysis in static timing analysis (STA) for semiconductor design. As designers, we understand the importance of ensuring accurate timing in digital circuits to achieve optimal performance and reliability. In this article, we will explore how STA plays a crucial role in validating timing constraints and detecting potential timing violations that can impact circuit functionality.

Static Timing Analysis involves analyzing all possible timing paths in a digital circuit to determine if the circuit can operate at the desired clock frequency. By considering factors such as timing constraints, signal arrival times, and required arrival times, we can identify critical paths and optimize the circuit’s timing to meet the required specifications.

Throughout this article, we will delve into the different types of timing paths involved in STA, the process of performing static timing analysis, and the significance of timing paths in the design flow. We will also discuss the role of STA in achieving timing closure and optimizing circuit performance.

Join us as we explore the world of worst-case timing analysis in STA and discover how it enhances the overall performance and efficiency of semiconductor designs.

Table of Contents

Importance of Timing Paths in STA

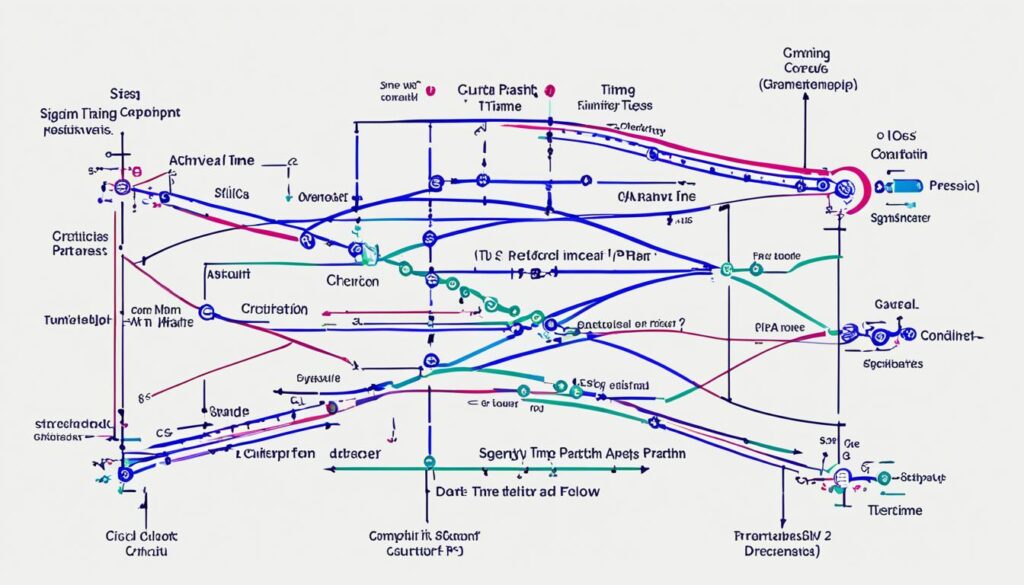

Timing paths are a critical aspect of Static Timing Analysis (STA) as they play a vital role in ensuring the proper functioning of digital circuits. These paths represent the routes through which data flows within a circuit, and analyzing them thoroughly is essential for validating the timing performance.

Data Paths

Data paths are one type of timing path that need to be carefully analyzed during STA. They depict the flow of data from input ports to output ports or between registers. By examining data paths, we can verify if the data arrives at its intended time, ensuring the circuit operates correctly.

Clock Paths

Clock paths are another significant type of timing path that demands attention during STA. They focus on the timing of the clock signals within the circuit. By analyzing clock paths, we can identify any delays or errors related to the clock timing, ensuring that the circuit functions synchronously and reliably.

Clock Gating Paths

Clock gating paths represent a specific type of timing path that deserves special consideration during STA. These paths explore the timing implications of clock gating elements, which are used to optimize power consumption in integrated circuits. By analyzing clock gating paths, we can ensure that the clock gating elements do not introduce unwanted delays or timing violations.

Asynchronous Paths

In addition to data paths and clock paths, STA also analyzes asynchronous paths within a digital circuit. Asynchronous paths refer to the timing of signals that are not synchronized with the clock. By examining asynchronous paths, we can identify any timing issues that may arise due to the lack of clock synchronization, ensuring the overall timing performance of the circuit.

During timing analysis, specific checks are performed to validate the timing paths and identify any potential violations. Setup checks ensure that the data is stable before the clock edge, while hold checks ensure that the data remains stable after the clock edge. These checks are essential for verifying the robustness and reliability of the circuit.

Propagation delay and transition time are key factors considered during timing analysis. Propagation delay measures the time it takes for a signal to travel from one point to another in the circuit, while transition time measures the time it takes for a signal to change from one logic level to another. Both of these factors have a direct impact on the timing performance of the circuit and must be accurately evaluated during STA.

In summary, timing paths are vital components in Static Timing Analysis as they represent the routes through which data flows in a digital circuit. By analyzing these paths and performing setup checks, hold checks, and considering propagation delay and transition time, we can validate the timing performance of the circuit and ensure its proper functioning.

The Process of Static Timing Analysis

Static Timing Analysis (STA) is an essential step in the chip design process to ensure the timing accuracy of a digital circuit. By analyzing the timing paths, identifying critical paths, and generating a timing report, STA plays a vital role in achieving timing closure and optimization.

STA is a multi-stage process that is performed after various design steps to validate and optimize the timing of a digital circuit. Let’s explore each stage:

1. RTL Design

STA begins after Register Transfer Level (RTL) design, where the design is represented using high-level hardware languages, such as VHDL or Verilog. At this stage, timing analysis is not possible due to the lack of timing information related to gates and interconnects.

2. Gate-Level Netlist Synthesis

After RTL design, the circuit is transformed into a gate-level netlist, representing the circuit’s structure using gates and flip-flops. STA is performed at this stage to ensure basic setup and hold checks are met.

3. Logic Optimization

Logic optimization techniques like technology mapping or retiming can significantly impact circuit timing. STA is performed after logic optimization to identify critical paths and determine if any timing violations exist.

4. Physical Design

In the physical design stage, which includes placement and routing, STA considers the placement of gates and the routing of interconnects. Timing paths are analyzed to account for interconnect delays and clock path delays.

5. Parasitic Extraction and Signal Integrity Analysis

STA continues after parasitic extraction, which considers the impact of parasitic elements, such as resistance and capacitance, on the circuit’s timing. Signal integrity analysis is also performed to ensure the signal quality is maintained within acceptable levels.

6. Timing Optimization Techniques

STA generates a timing report that highlights any timing violations found in the circuit. To achieve timing closure, timing optimization techniques are applied, including timing-driven placement, timing-driven routing, and physical synthesis.

Example Timing Report

| Critical Path | Delay (ns) |

|---|---|

| Path A | 5.6 |

| Path B | 4.2 |

| Path C | 7.8 |

The timing report provides crucial insights into the critical paths of the circuit, indicating the longest delays. Designers can use this information to prioritize optimization efforts in the timing closure process.

Static Timing Analysis is a fundamental step in semiconductor design, allowing us to validate the timing performance of digital circuits and optimize them for better circuit performance and reliability.

Types of Timing Paths in STA

Static Timing Analysis (STA) involves analyzing different types of timing paths in a digital circuit to ensure proper timing. These timing paths play a crucial role in determining the flow of data and the behavior of clock signals within the circuit.

Data Path

A data path represents the flow of data from the input ports to the output ports or between registers in a circuit. It is important to analyze the timing of data paths to ensure that the data arrives at the intended time, minimizing any potential timing violations.

Clock Path

A clock path analyzes the timing of the clock signals within the circuit. It includes the clock distribution network and any clock conditioning circuits. Analyzing the clock path helps identify potential timing violations and ensures that the clock signals are properly synchronized with the data flow.

Clock Gating Path

Clock gating is a technique used to conserve power by selectively disabling clock signals to specific circuit elements. Analyzing the timing implications of clock gating paths helps ensure that clock gating is correctly implemented and that no timing violations occur due to the gating mechanism.

Asynchronous Path

An asynchronous path considers the timing of signals that are not synchronized with the clock. These signals can introduce timing challenges and require careful analysis to ensure that they do not impact the overall timing of the circuit.

Critical Path

A critical path in a digital circuit is the path with the longest delay. It determines the maximum operating frequency of the circuit. Analyzing the critical path is essential for identifying and optimizing the timing constraints to achieve the desired performance.

False Path

A false path is a path that does not propagate any data. These paths do not contribute to the overall timing of the circuit and can be safely ignored during the static timing analysis process.

Multi-cycle Path

A multi-cycle path is a path that takes more than one clock cycle to propagate data. These paths require special consideration during timing analysis to ensure that the data is correctly synchronized across multiple clock cycles.

Thoroughly analyzing each type of timing path is crucial for ensuring proper timing in a digital circuit. By identifying critical paths, optimizing timing constraints, and addressing potential timing violations, designers can optimize the circuit’s performance and achieve timing closure.

Performing Static Timing Analysis in the Design Flow

Static Timing Analysis (STA) is an integral part of the Very Large Scale Integration (VLSI) circuit design flow. It is a crucial step in ensuring the timing integrity of digital circuits. STA is performed at multiple stages throughout the design flow to verify and optimize the timing of the circuit.

Starting with RTL Design

The design flow begins with Register Transfer Level (RTL) design. At this stage, timing verification is not possible due to a lack of timing information. However, the RTL design serves as the starting point for subsequent stages in the design flow.

Gaining Timing Insights after Gate-Level Netlist Synthesis

After the RTL design, the next step in the design flow is gate-level netlist synthesis. At this stage, STA can be performed to check basic setup and hold violations. The netlist represents the circuit in terms of logic gates and their interconnections, providing the necessary information for timing analysis.

Identifying Critical Paths after Logic Optimization

Logic optimization is a crucial step in improving circuit performance and reducing power consumption. Following logic optimization, STA is performed once again to identify critical paths. Critical paths are the longest paths in the circuit that determine its maximum delay. Optimizing these critical paths is essential for achieving better timing performance.

Considering Interconnect and Clock Path Delays after Placement and Routing

Placement and routing are critical stages in physical design, where the circuit’s components are mapped onto the physical layout. At this stage, STA analyzes interconnect delays and clock path delays. Interconnect delays account for the time taken for signals to propagate through wires, while clock path delays evaluate the timing of clock signals within the circuit.

Obtaining Accurate Timing Data after Detailed Routing and Parasitic Extraction

After detailed routing and parasitic extraction, STA is once again performed to obtain accurate timing data. Detailed routing takes into account the physical characteristics of the circuit’s components and minimizes wirelength to reduce delays. The parasitic effects associated with interconnects, such as resistance and capacitance, are considered during parasitic extraction, providing a more precise timing analysis.

| Stage | Timing Analysis Process |

|---|---|

| RTL Design | No timing verification, but serves as a starting point |

| Gate-Level Netlist Synthesis | Basic setup and hold violation checking |

| Logic Optimization | Identification of critical paths |

| Placement and Routing | Analysis of interconnect and clock path delays |

| Detailed Routing and Parasitic Extraction | Accurate timing analysis considering physical characteristics and parasitic effects |

The timing report generated by STA at each stage of the design flow serves as a valuable tool for achieving timing closure. Timing closure refers to the process of meeting all the required timing specifications for a digital circuit.

By utilizing timing optimization techniques such as timing-driven placement, timing-driven routing, and physical synthesis, designers can fine-tune the circuit’s timing and ensure it operates within the desired timing limits.

Performing Static Timing Analysis throughout the VLSI circuit design flow is essential for verifying and optimizing the timing of a digital circuit. It ensures that the circuit’s performance meets the required specifications and achieves timing closure.

Conclusion

In conclusion, Static Timing Analysis (STA) plays a crucial role in semiconductor design by validating the timing performance of digital circuits. By ensuring that data arrives at the intended time, STA helps improve circuit performance and reliability. Through the process of timing validation, optimization, and closure, STA identifies and optimizes critical paths, resulting in enhanced circuit efficiency.

By performing STA at different stages of the chip design process, we can ensure that our circuits meet timing requirements and operate reliably in real-world applications. STA helps us achieve timing closure by analyzing timing paths, identifying potential timing violations, and generating timing reports. These reports provide valuable insights into the circuit’s timing characteristics and serve as a guide for further optimizations.

With the constant evolution of semiconductor technology, the importance of Static Timing Analysis cannot be overstated. It allows us to achieve robust circuit performance and meet the increasing demands of modern electronic devices. By leveraging the power of STA, we can design circuits that not only meet timing specifications but also deliver optimal performance in terms of speed, power consumption, and overall efficiency.