Welcome to our series on Verilog for RTL Synthesis. In this comprehensive guide, we will explore the vital role that Verilog plays in the digital design and hardware description process. Whether you’re a seasoned engineer or just starting out in the field, understanding Verilog is crucial for optimizing your hardware solutions.

The world of hardware design relies heavily on Verilog, a hardware description language that allows designers to specify the behavior and structure of digital systems. Verilog serves as the bridge between the high-level design and the physical implementation, enabling engineers to express complex ideas in a concise and efficient manner.

RTL Synthesis, on the other hand, is the process of transforming the Register Transfer Level (RTL) description of a design into a gate-level representation, known as a netlist. This netlist forms the basis for the subsequent steps in the digital design flow, such as placement and routing, leading to the physical realization of the hardware.

Throughout this series, we will cover everything you need to know about Verilog for RTL Synthesis. From understanding Verilog as a hardware description language to coding guidelines, verification techniques, and advanced features for optimization, we’ll equip you with the knowledge and skills to excel in the world of digital design.

So, let’s dive in and explore the exciting world of Verilog for RTL Synthesis together!

Table of Contents

Understanding Verilog as a Hardware Description Language

To begin our exploration of Verilog for RTL Synthesis, it is important to understand Verilog as a hardware description language. Verilog is a high-level programming language used for the design, modeling, and simulation of digital systems. It allows engineers to specify the behavior and structure of electronic systems, enabling the synthesis of complex hardware designs.

Verilog, also known as a Hardware Description Language (HDL), provides a concise and efficient way to describe the functionality and interconnections of electronic circuits. It allows designers to represent hardware components, such as gates, registers, and modules, using a set of predefined keywords and constructs. These constructs enable the expression of sequential and combinational behavior within the design, facilitating the synthesis of the desired circuit.

As a HDL, Verilog serves as a bridge between the high-level design description and the physical implementation of the hardware. It allows designers to model abstract concepts, such as functional blocks and signal paths, in a precise and structured manner. By describing the design at a higher level of abstraction, engineers can focus on the functionality and behavior of the circuit, rather than the low-level implementation details.

Verilog offers several advantages as a hardware description language:

- Modularity: Verilog enables the creation of reusable and modular design components, allowing for efficient design reuse and faster development cycles.

- Conciseness: Verilog provides a concise syntax that allows engineers to express complex circuit behavior in a compact and readable form.

- Suitability for Synthesis: Verilog is specifically designed for synthesis, meaning that designs described in Verilog can be automatically transformed into a physical implementation, such as a netlist, by a synthesis tool.

- Simulation Capabilities: Verilog supports powerful simulation features that allow designers to verify and debug their designs before synthesis and implementation.

Understanding Verilog as a hardware description language is crucial for leveraging its capabilities to design and synthesize complex digital systems. In the next sections, we will explore the details of RTL synthesis, Verilog coding guidelines, verification techniques, and advanced features that further enhance the overall design process.

| Advantages of Verilog |

|---|

| Modularity |

| Conciseness |

| Suitability for Synthesis |

| Simulation Capabilities |

Introduction to RTL Synthesis

RTL (Register Transfer Level) Synthesis is a crucial step in the digital design flow. It plays a fundamental role in transforming high-level hardware descriptions into optimized netlists. This section provides an overview of RTL Synthesis and its significance in the design process.

RTL Synthesis serves as a bridge between the high-level hardware description, typically written in a hardware description language like Verilog, and the final synthesizable representation of the design. It involves translating the behavioral description of the hardware into a register transfer level representation, which consists of interconnected registers and combinational logic.

The main goal of RTL Synthesis is to optimize the design by improving performance, area utilization, and power consumption. It achieves this by automatically transforming the RTL description into a gate-level netlist, which can be further processed for physical implementation and manufacturing.

During RTL Synthesis, the design is analyzed, and optimizations are applied to reduce the number of logic gates, minimize the routing complexity, and improve the overall performance. These optimizations include technology mapping, logic folding, constant propagation, and resource sharing.

RTL Synthesis enables design exploration and trade-offs. Different design constraints and objectives can be considered to achieve the desired balance between performance, area, and power consumption. Through iterative synthesis, designers can fine-tune their designs to meet specific requirements and constraints.

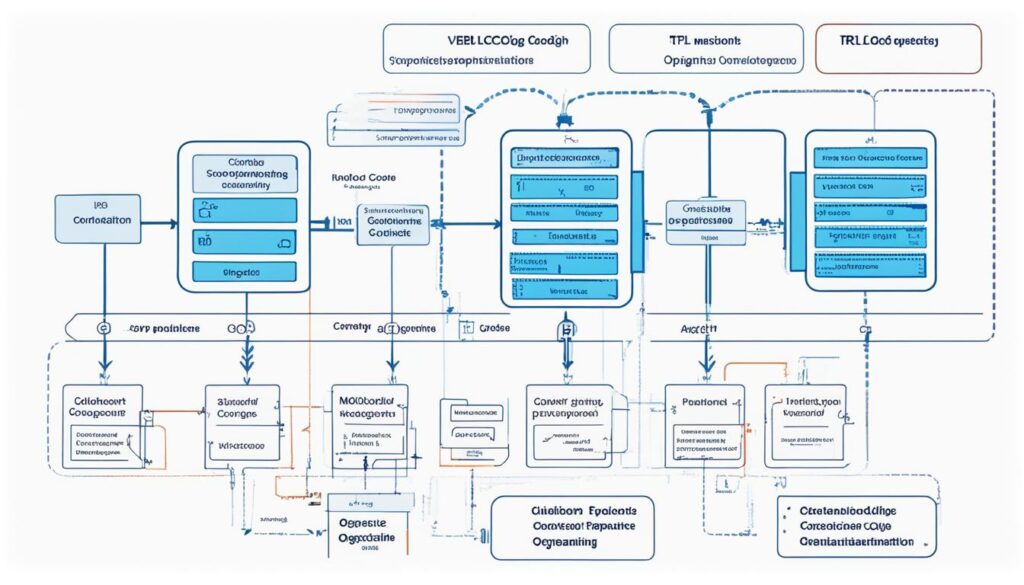

RTL Synthesis Workflow

The RTL Synthesis process typically follows these steps:

- Pre-processing: The input RTL description is analyzed, and any required transformations or modifications are performed.

- Elaboration: The design is elaborated, and the required hardware components are identified.

- High-level synthesis: The RTL description is transformed into a behavioral representation, which includes data flow and control flow.

- Logic synthesis: The behavioral description is further refined into a gate-level netlist that is optimized for the target technology.

- Post-processing: The synthesized netlist is analyzed and any additional optimizations or transformations are applied.

Benefits of RTL Synthesis

The adoption of RTL Synthesis brings several benefits to the digital design process:

- Higher productivity: RTL Synthesis automates the process of converting high-level hardware descriptions into optimized netlists, reducing manual effort and increasing productivity.

- Improved design quality: By employing RTL Synthesis, designers can leverage advanced optimization techniques to improve design quality, meeting performance and power requirements.

- Design exploration and optimization: RTL Synthesis allows designers to explore different design alternatives and trade-offs, enabling them to optimize their designs based on specific constraints and objectives.

- Efficient physical implementation: The gate-level netlist generated by RTL Synthesis serves as the foundation for subsequent steps in the design flow, such as physical synthesis, placement, and routing.

RTL Synthesis is an essential component of modern digital design flows. It empowers designers to efficiently transform high-level hardware descriptions into optimized netlists, laying the groundwork for successful hardware implementation.

Verilog Coding Guidelines for RTL Synthesis

Writing Verilog code that is RTL synthesis-friendly is crucial for achieving optimal hardware designs. In this section, we will discuss the important coding guidelines and best practices that need to be followed while using Verilog for RTL Synthesis.

Coding Guidelines

When writing Verilog code for RTL Synthesis, it is essential to adhere to certain guidelines to ensure a smooth synthesis process and maximize the efficiency of the resulting hardware design. The following coding guidelines are recommended:

- Use descriptive signal and variable names: Choose meaningful names that accurately represent the functionality and purpose of the signals and variables. Avoid using generic names or abbreviations that may cause confusion.

- Follow proper coding style: Maintain consistent indentation, use sensible spacing, and follow a clear and readable coding style. This improves code understanding, readability, and maintainability.

- Avoid inferring latches: Latches are undesirable and can lead to unpredictable behavior. Make sure all signals have well-defined values in all possible scenarios.

- Minimize the use of procedural blocks: Excessive procedural blocks can hinder synthesis and cause unexpected delays. Use procedural blocks sparingly and only when necessary.

- Avoid race conditions: Ensure that there are no timing-related conflicts or race conditions in the design. Pay attention to signal timing and use appropriate synchronization techniques where required.

- Eliminate unnecessary complexity: Simplify the design by removing redundant logic and optimizing complex expressions. This improves synthesis results and reduces the chances of errors.

Best Practices

In addition to coding guidelines, certain best practices can further enhance the effectiveness of Verilog code for RTL Synthesis:

- Use proper hierarchy: Divide the design into manageable modules with clearly defined interfaces. This promotes modularity, reusability, and easier debugging.

- Document the code: Add comments and descriptive documentation to explain the purpose, functionality, and assumptions of the code. This facilitates collaboration, maintenance, and future modifications.

- Perform regular simulations: Conduct thorough simulations to verify the correctness and functionality of the design before undergoing synthesis. Simulations can help identify and resolve any potential issues or bugs early in the development process.

- Stay updated with technology advancements: Keep up with the latest advancements and updates in Verilog and RTL Synthesis methodologies. This ensures that the code remains compatible with the latest tools and techniques, leading to more efficient and optimized designs.

By adopting these coding guidelines and best practices, engineers can create Verilog code that is well-suited for RTL Synthesis, resulting in optimized and reliable hardware designs.

| Guidelines | Best Practices |

|---|---|

| Use descriptive signal and variable names | Use proper hierarchy |

| Follow proper coding style | Document the code |

| Avoid inferring latches | Perform regular simulations |

| Minimize the use of procedural blocks | Stay updated with technology advancements |

| Avoid race conditions | |

| Eliminate unnecessary complexity |

Verification Techniques for RTL Synthesis

In the process of RTL synthesis, it is crucial to verify the correctness and functionality of the RTL design before proceeding with synthesis. By employing various verification techniques and methodologies, we can ensure that the design meets the required specifications and will perform as intended. In this section, we will explore some of the common verification techniques used in conjunction with Verilog for RTL synthesis.

One widely used technique is Simulation-Based Verification. This involves creating a testbench environment to stimulate the RTL design with different input scenarios and verify the output against expected results. Simulation tools such as ModelSim and Questasim are commonly used for this purpose, allowing us to identify and debug any design issues.

Formal Verification is another powerful technique that involves mathematical-based analysis to prove the correctness of a design. By examining all possible input combinations, formal verification tools such as JasperGold and Formal Pro can rigorously check the design for potential bugs, functional errors, and corner-case scenarios. This technique provides a higher level of confidence in the correctness of the RTL design.

Assertion-Based Verification is a technique that involves specifying properties or assertions about the design behavior. These assertions are then checked using tools such as Cadence Incisive or Aldec Riviera-PRO to ensure that the design meets the specified requirements. Assertions can be written in SystemVerilog or SVA (SystemVerilog Assertions) and help in catching design errors or violations during simulation.

Code Coverage and Functional Coverage are essential techniques used to measure the completeness of the verification process. Code coverage tools such as Mentor Questa Cover and Aldec Riviera-PRO Coverage analyze the RTL code and determine the percentage of code that has been exercised during simulation. Functional coverage, on the other hand, focuses on verifying specific functional scenarios defined by coverage models. By utilizing these techniques, we can ensure that our verification efforts are thorough and comprehensive.

To summarize, verification techniques are critical in ensuring the correctness and functionality of RTL designs during the synthesis process. By employing simulation-based verification, formal verification, assertion-based verification, and code and functional coverage analysis, we can confidently validate the RTL design before proceeding with synthesis.

Advanced Features and Optimization in Verilog RTL Synthesis

In Verilog RTL Synthesis, advanced features and optimization techniques play a vital role in enhancing the efficiency and performance of the synthesized hardware. By harnessing these capabilities, we can achieve optimal results in the digital design process.

One of the advanced features in Verilog is parameterization, which allows us to define and customize parameters within the code. With parameterization, we can easily modify and adapt the design to meet specific requirements without the need for extensive code changes. This flexibility simplifies the design iteration process and enables faster development cycles.

Another powerful feature is generate blocks, which provide the ability to create dynamic and reusable hardware components. By using generate blocks, we can generate multiple instances of a module based on certain conditions or parameters. This feature greatly enhances code reusability and enables efficient design implementation.

Verilog also offers various optimization techniques to improve the performance and area utilization of the synthesized hardware. One such technique is resource sharing, where common hardware resources are shared among different parts of the design to minimize redundant elements. Resource sharing reduces area requirements and improves overall performance.

Additionally, Verilog supports retiming, which involves the optimization of the clock cycle assignments for synchronous circuits. By redistributing the pipeline stages and delaying the critical paths, we can achieve improved timing constraints and better performance.

Furthermore, logic folding is an optimization technique that reduces the number of logic gates by merging similar and adjacent logic operations. This results in a more compact and efficient hardware design, reducing area utilization and power consumption.

Lastly, Verilog RTL Synthesis provides technology mapping capabilities that enable the mapping of the RTL design onto specific target technologies. This process involves the selection of appropriate libraries and cells to optimize the design for a particular technology, taking into consideration factors such as area, power, and performance requirements.

Advantages of Advanced Features and Optimization in Verilog RTL Synthesis

By leveraging the advanced features and optimization techniques available in Verilog, we can achieve numerous benefits in RTL Synthesis:

- Improved performance and efficiency of the synthesized hardware

- Enhanced code reusability and faster design iteration cycles

- Reduced area utilization and power consumption

- Optimal timing constraints and better overall performance

- Efficient mapping onto specific target technologies

Overall, the advanced features and optimization techniques in Verilog RTL Synthesis empower designers to create highly optimized and efficient hardware designs, enabling the realization of cutting-edge solutions in the field of digital design.

Conclusion

In conclusion, Verilog for RTL Synthesis is an essential aspect of digital design and hardware description. By following the recommended coding guidelines, engineers can ensure that their Verilog code is optimized for RTL synthesis. This includes using proper naming conventions, avoiding non-synthesizable constructs, and utilizing design patterns that promote efficient hardware generation.

Implementing appropriate verification techniques is another crucial step in the RTL synthesis process. By thoroughly testing the RTL design, engineers can identify and fix any functional issues before synthesis, reducing the likelihood of costly errors in the final hardware implementation. Techniques such as simulation, formal verification, and hardware emulation play a vital role in achieving reliable, bug-free designs.

Furthermore, taking advantage of the advanced features and optimization techniques offered by Verilog can significantly improve the performance and efficiency of the synthesized hardware. This includes leveraging pipelining, resource sharing, and advanced data types to minimize critical path delays and reduce area requirements.

Overall, Verilog for RTL Synthesis empowers designers to create high-quality, optimized hardware designs. By following best practices, adhering to coding guidelines, and leveraging advanced features, engineers can successfully navigate the RTL synthesis process and achieve optimal results.