Welcome to our article on setup and hold time in Flip-Flop, two critical parameters in the design of reliable digital circuits. In this piece, we will delve into the intricacies of these parameters and explore their significance in ensuring optimal circuit performance.

Flip-Flops are fundamental building blocks in digital circuits, playing a crucial role in storing and transferring data. By understanding the concept of setup and hold time, designers can ensure the proper functioning of Flip-Flops, minimizing the risk of errors and failures.

In the following sections, we will explain the definitions of setup and hold time, discuss their relationship, and explore the design considerations necessary for meeting these constraints. We will also emphasize the importance of adhering to setup and hold time specifications to guarantee the reliable operation of digital circuits.

By the end of this article, you will have a comprehensive understanding of setup and hold time in Flip-Flop, empowering you to design robust digital circuits that meet the highest standards of performance. So, let’s dive in!

Table of Contents

What is a Flip-Flop?

A Flip-Flop is a fundamental component in digital circuits that is widely used for storing and manipulating binary data. It is a sequential circuit element that can store a single bit of information, represented as either a 0 or a 1.

Flip-Flops play a crucial role in modern electronics and are essential for various applications, such as data storage, memory elements, and synchronization circuits. They are the building blocks of more complex digital systems, enabling the creation of flip-flop-based registers, counters, and other sequential logic circuits.

Flip-Flops are composed of logic gates and operate based on clock signals. The clock input determines when the data input is latched and stored, and the stored value remains steady until the next clock pulse. This characteristic makes Flip-Flops capable of retaining information, even when the input changes. It provides stability and enables the storage of data in sequential order.

There are various types of Flip-Flops, including D Flip-Flops, JK Flip-Flops, SR Flip-Flops, and T Flip-Flops. Each type has its own unique characteristics and applications, but they all share the common trait of being able to store and manipulate binary data.

Understanding the basics of Flip-Flops is essential for anyone working with digital circuits. These versatile components provide the foundation for creating complex and reliable digital systems, making Flip-Flops a crucial element in modern electronics.

Understanding Setup Time

In digital circuits, the concept of setup time plays a crucial role in ensuring reliable circuit operation. Setup time refers to the minimum duration that the input signal to a flip-flop should be stable before the clock transition. It is the time required for the input signal to settle down and be sampled correctly by the flip-flop.

During setup time, any changes in the input signal can lead to unpredictable outputs, resulting in potential errors in the circuit operation. Therefore, meeting the setup time requirement is vital to ensure proper flip-flop functionality.

To better understand the impact of setup time, let’s take a closer look at how it is measured. The setup time measurement process involves capturing the arrival time of the input signal relative to the clock edge. This measurement helps in determining whether the input signal is stable long enough before the clock edge transition.

Measurement Process for Setup Time

To measure setup time, a test setup is typically used, consisting of a flip-flop, input signal source, and a clock signal generator. The input signal is applied to the flip-flop, while the clock signal governs the transition of the flip-flop’s state.

The input signal is varied in time, and the clock transition is monitored. By observing the output response of the flip-flop, the setup time can be determined based on the point where changes in the input signal start to affect the output stability.

This measurement process not only ensures reliable circuit operation but also helps in selecting the appropriate flip-flop for specific design requirements, considering the setup time specifications that must be met.

Table 1 below provides a comparison of setup time specifications for commonly used flip-flops:

| Flip-Flop Type | Setup Time Specification |

|---|---|

| D Flip-Flop | 1 ns |

| T Flip-Flop | 500 ps |

| JK Flip-Flop | 2 ns |

Table 1: Setup Time Specifications for Commonly Used Flip-Flops

Having a clear understanding of setup time and its impact is crucial for designing robust and reliable digital circuits. By ensuring that the input signal remains stable for the required duration before the clock transition, designers can mitigate potential errors and ensure optimal circuit performance.

Exploring Hold Time

Hold time plays a significant role in ensuring the proper functionality of Flip-Flops in digital circuits. It refers to the minimum amount of time that the input signals must be held stable after the clock edge for the data to be correctly latched into the Flip-Flop.

During the hold time period, the input signals must not change to avoid any invalid output or metastability issues. If the inputs change too early, the Flip-Flop might enter an unstable state, leading to unpredictable results.

Hold time is critical in high-speed circuits where signal propagation delays can vary, causing variations in setup times. By ensuring a sufficient hold time, designers can mitigate the effects of these delays and maintain the stability of the circuit.

Importance of Hold Time

Hold time is essential for preventing data corruption and maintaining the integrity of digital signals. Failure to meet the hold time requirement can result in a phenomenon known as hold-time violation, which can lead to race conditions and erroneous outputs.

Hold-time violations occur when the input signals change before the hold time requirement is met, causing the outputs to become unpredictable. These violations can propagate through the circuit, potentially causing errors in subsequent stages.

By ensuring an adequate hold time, designers can eliminate the risk of hold-time violations and guarantee reliable circuit performance. This is particularly crucial in synchronous designs where Flip-Flops are used extensively.

It is important to note that hold time and setup time are interrelated. Satisfying both setup and hold time requirements is essential for the Flip-Flop to function correctly and provide stable outputs.

Hold Time Constraints

The hold time constraint is typically provided by the manufacturer of the Flip-Flop and is specified in the datasheet of the device. It defines the minimum time that the input signals must be held stable after the clock edge for proper operation.

Designers must adhere to the hold time constraint to guarantee reliable circuit behavior. This involves considering propagation delays, signal variations, and other parameters that can affect the hold time margin.

Table: Hold Time Constraints for Common Flip-Flop Families

| Flip-Flop Family | Hold Time Constraint |

|---|---|

| D Flip-Flop | 1 ns |

| JK Flip-Flop | 1 ns |

| T Flip-Flop | 1 ns |

Meeting the hold time constraints is crucial for ensuring reliable circuit operation and preventing timing issues. Failure to satisfy these constraints can result in unpredictable behavior and compromise the functionality of the digital system.

The Relationship between Setup and Hold Time

Setup and hold time are critical parameters in the design of digital circuits, particularly in the operation of flip-flops. Understanding the relationship between these two parameters is essential for ensuring the stability and reliability of these circuits.

Setup time refers to the minimum amount of time that a data input signal needs to be stable before the clock signal arrives. It allows the flip-flop to capture the input correctly and prevent data corruption. On the other hand, hold time refers to the minimum amount of time that the data input signal needs to remain stable after the clock signal arrives. It ensures that the captured data is not affected by any changes in the input signal during the clock transition.

The relationship between setup and hold time is crucial in maintaining the integrity of digital circuits. When the setup time is insufficient, the flip-flop may capture an incorrect or distorted version of the input data. Similarly, if the hold time is not met, the captured data may become corrupted or lost before the next clock cycle.

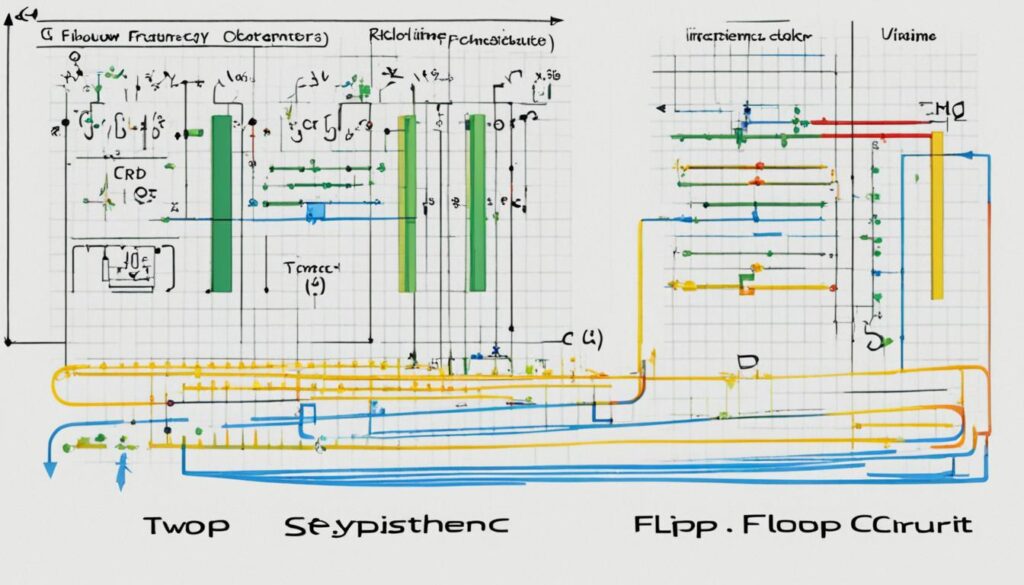

Their relationship can be visualized through the timing diagram, which illustrates the timing constraints on the input and clock signals. By analyzing this diagram, designers can determine the appropriate setup time and hold time values to ensure proper circuit operation.

It is important to note that the relationship between setup and hold time is not fixed and can vary depending on the specific flip-flop design and operating conditions. Designers must carefully consider these parameters and their interdependence to guarantee the reliable functionality of digital circuits.

Design Considerations for Setup and Hold Time

When dealing with setup and hold time in digital circuit design, there are several key considerations that designers need to keep in mind. These considerations play a crucial role in ensuring optimal circuit performance and reliability. Here, we will explore some of the most important design considerations for setup and hold time.

Clock Skew

One critical factor to consider is clock skew, which refers to the discrepancy in arrival times of the clock signal at different circuit elements. Clock skew can adversely affect setup and hold time by causing data to be captured inaccurately. To minimize clock skew, designers should implement strategies such as balanced clock tree synthesis and clock distribution techniques.

Signal Integrity

Signal integrity is another vital aspect to consider when dealing with setup and hold time. Proper signal integrity measures, such as impedance matching and noise reduction techniques, help in preserving accurate data capture and minimizing timing violations. Careful PCB layout design with controlled trace lengths can also contribute to improved signal integrity.

Delay Budgeting

Delays introduced by various components in a circuit can impact setup and hold time. Designers must allocate an appropriate delay budget to account for these delays and ensure that setup and hold constraints are met. This involves carefully analyzing the delays introduced by logic gates, interconnects, and flip-flops in the circuit.

Timing Analysis

Performing thorough timing analysis is crucial to identify potential timing violations and ensure that setup and hold time requirements are met. By employing advanced timing analysis tools, designers can accurately predict and optimize setup and hold time issues in their designs.

It is essential to strike a balance between reducing setup and hold time violations without compromising circuit performance. Designers should also consider the specific requirements of the application, such as operating frequency and power constraints, when making design decisions.

By carefully considering these design considerations for setup and hold time, designers can effectively reduce timing violations and optimize the performance of their digital circuits.

| Design Considerations | Explanation |

|---|---|

| Clock Skew | Discrepancy in arrival times of the clock signal at different circuit elements. Minimizing clock skew improves setup and hold time accuracy. |

| Signal Integrity | Preserving accurate data capture by ensuring proper impedance matching, noise reduction, and controlled PCB layout design. |

| Delay Budgeting | Allocating appropriate delay budget to account for delays introduced by logic gates, interconnects, and flip-flops. |

| Timing Analysis | Thorough analysis of timing violations and optimization of setup and hold time using advanced timing analysis tools. |

Importance of Meeting Setup and Hold Time Constraints

Ensuring the adherence to setup and hold time constraints is of utmost importance in the design and implementation of Flip-Flops. These constraints play a crucial role in maintaining the reliable and accurate operation of digital circuits. Failure to meet these specifications can lead to detrimental effects on circuit performance, resulting in potential system failures, signal integrity issues, and data corruption.

When setup time constraints are not met, it can result in improper latch control, causing data to be sampled before it has stabilized. This can lead to metastability, where the Flip-Flop’s output is in an unpredictable state, jeopardizing the integrity of subsequent circuit stages. Similarly, failing to meet hold time constraints can result in data corruption during the transition between clock cycles, leading to errors and system malfunctions.

To better understand the significance of meeting setup and hold time constraints, consider the following practical example:

| Scenario | Consequences |

|---|---|

| A Flip-Flop with insufficient setup time | – Data instability and unpredictable output – Signal integrity issues – Potential system failures |

| A Flip-Flop with inadequate hold time | – Data corruption during clock transitions – Errors and system malfunctions |

As shown in the example, disregarding the setup and hold time constraints can lead to severe consequences, jeopardizing circuit reliability and overall system functionality. Designers must recognize the criticality of these parameters and ensure their compliance throughout the development process to mitigate potential risks and guarantee the proper operation of digital circuits.

Achieving Optimal Performance

Meeting setup and hold time constraints is not only essential for preventing errors and malfunctions but also for achieving optimal circuit performance. By adhering to the specified timing constraints, designers can eliminate signal timing violations, minimize noise, and enhance the stability and accuracy of the digital system.

Furthermore, by carefully considering setup and hold time requirements during the design phase, designers can optimize the overall circuit performance, ensuring that data is reliably captured and retained by the Flip-Flops. This attention to detail enables systems to operate efficiently, leading to improved data integrity, reduced power consumption, and enhanced overall functionality.

In summary, meeting setup and hold time constraints is vital for establishing robust and reliable digital circuits. By prioritizing these timing specifications, designers can mitigate risks, minimize errors, and optimize performance, ultimately ensuring the seamless operation of digital systems.

Stay tuned for the finale!

Conclusion

In conclusion, this article has provided a comprehensive understanding of setup and hold time in Flip-Flop. By appreciating the importance of these parameters and paying careful attention to their constraints, designers can ensure the reliable and efficient functioning of digital circuits.