In the world of integrated circuit design, clock tree structures are key. They help distribute clock signals well. This is vital for digital components to work together smoothly.

The design of these structures affects a circuit’s performance and power use. There are several types, like the H-tree and balanced tree. Each aims to improve signal distribution and cut down on power use.

Clock Tree Synthesis (CTS) is a crucial step in circuit design. It comes after placement and before routing. It balances clock delays by adding buffers or inverters to paths.

The aim is to get clock signals to their destinations quickly and evenly. This is essential for digital logic to work right.

Table of Contents

Understanding Clock Tree Synthesis Fundamentals

Clock signals are vital in digital circuits, guiding data flow through flip-flops and latches. An effective system includes a clock source, the clock tree, and sink pins for sequential logic. These parts work together to keep the circuit running smoothly.

The Role of Clock Signals in Digital Design

Clock signals are the heart of digital circuits, making sure everything works together. They control when data is sampled and moved, keeping the system running smoothly. Good clock distribution is key to avoiding timing problems that can hurt the circuit’s performance.

Key Components of Clock Distribution

The clock network has three main parts: the clock source, the clock tree, and sink pins. The clock source, like a PLL or oscillator, creates the master clock. The clock tree spreads this signal to flip-flops and latches, the sink pins.

Importance of Clock Tree Balance

A balanced clock tree is essential for a digital circuit’s success. Clock Tree Synthesis (CTS) works to reduce delay, lower skew, and save power. It involves steps like clustering and power optimization to ensure all parts switch at the same time. This improves timing, power, and signal quality.

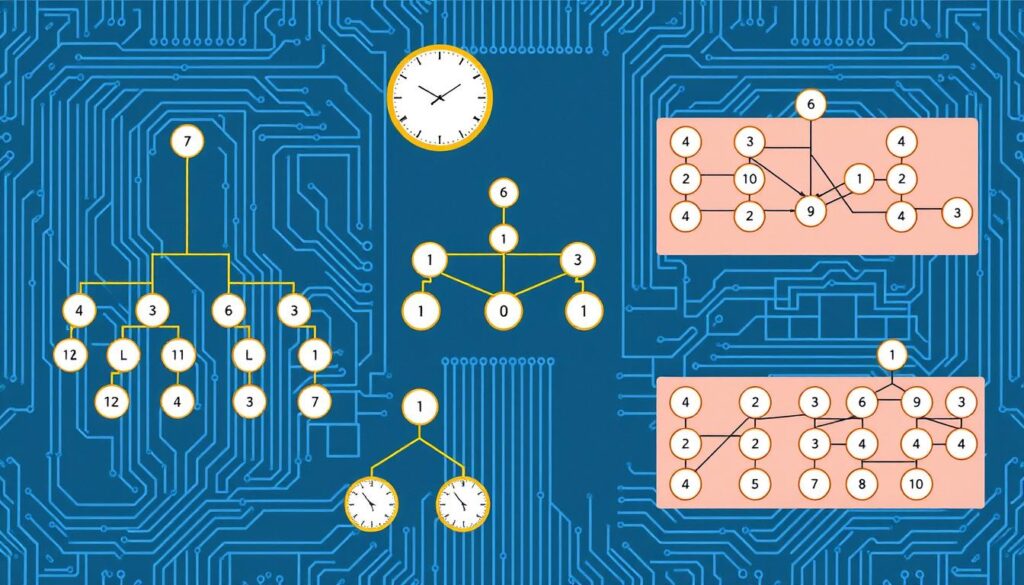

Major Clock Tree Structures

In digital design, getting clock signals to all parts of a circuit is key. It affects how well and reliably a circuit works. Clock tree structures help make sure everything in a system-on-chip (SoC) or application-specific integrated circuit (ASIC) is in sync. Let’s look at some main clock tree designs and where they’re used.

H-Tree Architecture and Applications

The H-tree is a common clock tree design. It’s great for scaling and is balanced. It works well for high-frequency needs, but it needs clock sinks that are powers of two. This can be tricky in some designs.

Clock Mesh Design Principles

The clock mesh is a newer design that’s big in high-speed processors. It’s a grid of lines that balances clocks well, perfect for GHz speeds. But, it uses more power and resources because of its complex structure.

Spine and Fishbone Structures

There are other clock tree designs too, like the spine and fishbone. The spine has a main trunk for clock distribution. The fishbone has a spine with branches. These designs are good for certain needs, like power and area.

Choosing a clock tree design depends on the circuit’s needs and goals. Knowing the good and bad of each design helps make clock networks better. This ensures digital systems work well and efficiently.

Clock Tree Performance Metrics

Creating a good clock distribution network is key in today’s digital circuits. Important metrics include clock latency, clock skew, clock slew, minimum pulse width, duty cycle, and clock power. It’s vital to understand and improve these to make designs fast and power-efficient.

Clock Latency: This metric includes both source and network latency. It’s crucial for the timing of the design. Reducing clock latency helps sequential elements work right and avoids timing issues.

Clock Skew: This is the difference in clock arrival times between different registers. It can cause timing failures. So, managing clock skew well is important during the design process.

Clock Slew: This is how fast the clock signal changes. It affects the power use of the design. Keeping clock slew low helps save power and ensures the circuit works well.

Minimum Pulse Width: This is how long the clock signal must last for sequential elements to work right. Making sure the pulse width is enough is key to avoiding errors.

Duty Cycle: This can get out of balance due to clock repeaters. A balanced duty cycle is necessary for the circuit to work properly.

Clock Power: This is a big part of the design’s power use. Using techniques like clock gating and smart buffer/inverter placement helps lower power use.

By focusing on these key metrics, designers can make clock distribution networks that are efficient and reliable. This meets the needs of today’s digital circuits.

Clock Tree Power Optimization Strategies

Reducing power in clock trees is key in digital design. Techniques like clock gating, multi-bit registers, and smart buffer placement help a lot. They cut down dynamic power without hurting circuit speed.

Clock Gating Techniques

Clock gating is a top power-saving method used in most designs. It turns off the clock to idle registers, saving about 20% of dynamic power. It also keeps leakage power and timing good. Though it adds about 2% area, it doesn’t slow down design and verification much.

Multi-bit Register Implementation

Using multi-bit registers is another power-saving trick. It combines several registers into one, cutting down area and clock pin capacitance. This makes the clock network more power-efficient.

Buffer and Inverter Placement

Where you put clock buffers and inverters matters a lot for power. Smart placement and sizing of these elements save power while keeping performance up. Tools help ensure the clock tree is efficient and balanced.

Source Links

- Clock Tree Synthesis in VLSI Physical Design

- Ultimate Guide: Clock Tree Synthesis – AnySilicon

- What is Clock Tree Synthesis?

- Clock Tree Synthesis – VLSITutor

- Clock tree synthesis and SoC clock distribution strategies

- CTS Clock Tree Synthesis

- Optimal Generalized H-Tree Topology and Buffering for High-Performance and Low-Power Clock Distribution

- A Tree Clock Data Structure for Causal Orderings in Concurrent Executions

- Clock Tree Optimization

- Clock Tree Optimization Methodologies for Power and Latency Reduction – Semiconductor Digest