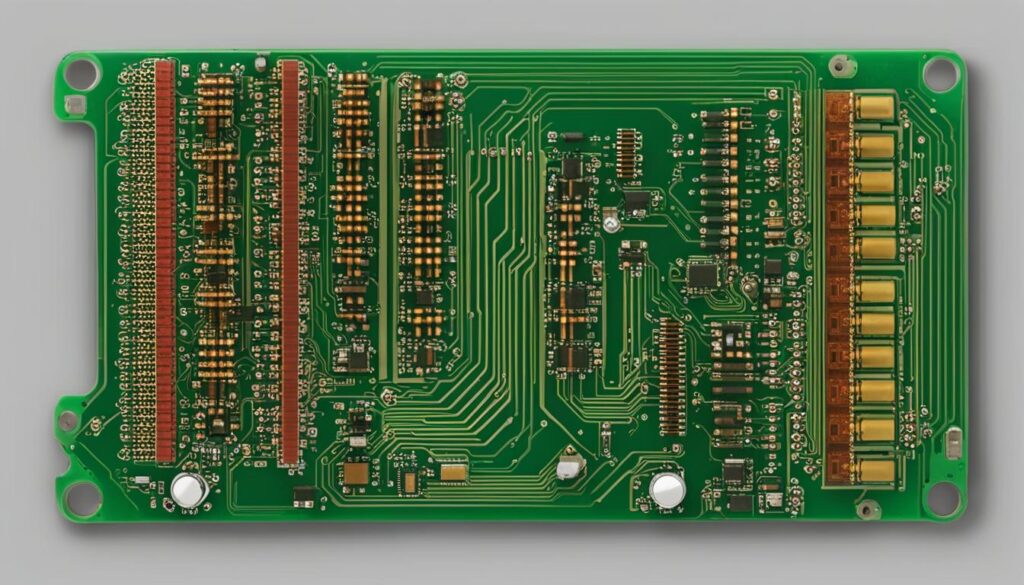

In digital circuit design, ensuring robust and reliable performance is crucial. One area that requires careful attention is clock domain crossing, the transfer of data between different clock domains. To achieve accurate timing and functionality, it is essential to apply appropriate timing constraints.

The use of timing constraints, such as set_false_path, set_clock_groups, set_net_delay, and set_max_skew, helps maintain the integrity of data transfer between clock domains. These constraints play a vital role in minimizing clock latency, ignoring false paths, controlling clock skew, and preventing timing violations.

By reviewing the SDC timing constraints and utilizing commands like set_false_path, set_clock_groups, set_net_delay, and set_max_skew, we can optimize the design for performance and ensure a robust digital circuit design. Let’s explore the guidelines and best practices for constraining clock domain crossings in more detail.

Table of Contents

Guidelines for Constrained Clock Domain Crossing

When constraining a clock domain crossing, it is important to follow specific guidelines to ensure proper functionality and reliable operation of the digital circuit. Here are some key guidelines to consider:

Review SDC Timing Constraints

Before applying constraints, it is crucial to review the SDC (Synopsys Design Constraints) timing constraints used in the design. This ensures that no set_false_path constraint exists between the two clock domains, as the set_false_path constraint has a higher precedence than other path-based constraints.

Remove False Paths with set_clock_groups

Instead of relying on set_false_path constraints, use set_clock_groups to explicitly define clock domains and remove false paths between them. The set_clock_groups command has a lower precedence than set_false_path, allowing false paths to be ignored during timing analysis.

Constrain Paths with set_net_delay

To minimize net lengths and ensure accurate timing analysis, use the set_net_delay constraint to explicitly constrain the paths between clock domains. This constrains the delay of the nets and improves timing analysis accuracy.

Control Clock Skews with set_max_skew

Controlling clock skews is crucial for the proper functioning of clock domain crossings. Use the set_max_skew constraint to limit clock skews within acceptable ranges. This ensures accurate synchronization and reliable data transfer between clock domains.

By implementing these guidelines using commands like create_clock, set_clock_groups, set_net_delay, and set_max_skew, designers can effectively constrain clock domain crossings and optimize the performance of their digital circuit designs.

| Command | Description |

|---|---|

create_clock |

Defines a clock signal in the design |

set_clock_groups |

Explicitly defines clock domains and removes false paths |

set_net_delay |

Constrains the delay of paths between clock domains |

set_max_skew |

Limits clock skews within acceptable ranges |

Single-bit and Multi-bit Clock Domain Crossing

In digital circuit design, clock domain crossings can be categorized into single-bit and multi-bit crossings. Understanding the differences between these two types is crucial for ensuring reliable data transfer between clock domains.

Single-bit Clock Domain Crossing

A single-bit clock domain crossing involves the transfer of a single bit of data between clock domains. This type of crossing is typically handled using a 2FF synchronizer.

A 2FF synchronizer is a common technique used to ensure proper synchronization of single-bit data transfers between different clock domains. It consists of two flip-flops (FF) connected in series, with the output of the first FF acting as the input to the second FF. This arrangement helps to capture and stabilize the input signal in the receiving clock domain, minimizing the risk of metastability issues.

The diagram above illustrates a 2FF synchronizer. The input signal, coming from the source clock domain, is captured by the first FF on the rising edge of the source clock. Then, the output of the first FF is captured by the second FF on the rising edge of the receiving clock, ensuring proper synchronization.

Multi-bit Clock Domain Crossing

A multi-bit clock domain crossing involves the transfer of multiple bits of data between clock domains. Unlike single-bit crossings, multi-bit crossings often require additional mechanisms to ensure data stability and synchronization.

A stability guard or handshake mechanism is commonly employed in multi-bit clock domain crossings. This mechanism uses a single-bit synchronizer, similar to the 2FF synchronizer, in both the source and receiving clock domains to ensure the stability of the logic state in the source domain.

One example of a handshake scheme for multi-bit crossings is the use of parallel buses. By dividing the multi-bit data into multiple single-bit signals and applying the 2FF synchronizer to each signal, parallel buses enable synchronized data transfer across clock domains.

Another approach is to use sets of individually synchronized signals for the multi-bit crossing. Each signal in the set is synchronized using a single-bit synchronizer, ensuring proper data synchronization between the clock domains.

Summary

In summary, clock domain crossings can be categorized into single-bit and multi-bit crossings. Single-bit crossings are typically handled using a 2FF synchronizer, while multi-bit crossings require stability guards or handshake mechanisms to ensure data stability and synchronization. Understanding these different types of crossings is essential for successful digital circuit design.

Importance of Timing Constraints in Clock Domain Crossing

When designing digital circuits, timing constraints are crucial in ensuring the proper functioning of clock domain crossing. These constraints play a critical role in ensuring that the paths between clock domains meet the required timing specifications, enabling the reliable transfer of data between different clock domains.

One of the key challenges in clock domain crossing is managing clock latency. Clock latency refers to the delay introduced when transferring data from one clock domain to another. Excessive clock latency can result in data corruption or improper synchronization, leading to system malfunction. By applying appropriate timing constraints, designers can optimize the clock latency and ensure accurate data transfer.

Another important aspect of timing constraints is avoiding false paths. False paths are signal paths that do not impact the overall functionality of the system. By setting appropriate timing constraints using commands like set_false_path, these false paths can be ignored during timing analysis. This simplifies the timing analysis process and allows designers to focus on critical paths, ensuring efficient use of resources.

Clock skew is another critical issue that can affect clock domain crossing. Clock skew refers to the variation in arrival times of clock signals among different clock domains. If not properly addressed, clock skew can lead to timing violations and unreliable data transfer. By defining precise timing constraints, such as using set_max_skew, designers can control clock skew and ensure consistent synchronization between clock domains.

Timing violations are undesirable conditions in clock domain crossing where the required timing specifications are not met. These violations can result in system failures, data corruption, or other performance issues. By applying proper timing constraints, such as constraining paths with set_net_delay, designers can minimize timing violations and optimize the overall performance of the system.

In summary, timing constraints are crucial for successful clock domain crossing. By carefully defining and implementing these constraints, designers can optimize clock latency, ignore false paths, control clock skew, and minimize timing violations. These practices ensure the robustness and reliability of digital circuit designs.

Conclusion

Clock domain crossing constraints are crucial for ensuring the robustness and reliability of digital circuit designs. By applying appropriate timing constraints, such as using set_false_path and set_clock_groups to remove false paths, constraining paths with set_net_delay, and controlling clock skews with set_max_skew, we can optimize the performance and functionality of our designs. These best practices in clock domain crossing help us create a robust and reliable digital circuit design.

By carefully reviewing the SDC timing constraints and employing the right techniques, we can address key challenges associated with clock domain crossing. Timing constraints play a pivotal role in guiding synthesis and physical implementation tools to optimize our design for performance and prevent timing violations. They help us eliminate excessive clock latency, ensure that false paths are ignored in analysis, and minimize the impact of clock skew on synchronization.

Designers must always consider timing constraints as an integral part of the digital circuit design process. By adhering to the best practices discussed, we can create digital circuits that are not only efficient but also robust and reliable. With clock domain crossing constraints in place, we can confidently navigate the challenges of digital circuit design, ensuring our designs meet timing specifications and operate flawlessly.