Welcome to our article on Primitive Gates and User-defined Modules in Verilog HDL design and simulation. In this comprehensive guide, we will explore the fundamental concepts of these building blocks and their significance in creating complex digital systems using Verilog.

Verilog HDL is a hardware description language widely used in the field of digital design and simulation. It allows designers to describe the behavior and structure of digital circuits, enabling efficient and accurate system-level modeling. By understanding the concepts of Primitive Gates and user-defined Modules, you will gain the necessary knowledge to design and simulate sophisticated digital systems.

Table of Contents

Understanding Primitive Gates

Primitive Gates serve as the fundamental building blocks of digital circuits. In this section, we will explore these essential components and delve into their behavior within Verilog.

Logic Gates

Logic gates are electronic devices that operate on one or more inputs to produce a single output based on predefined logical functions. They are categorized into different types, such as the AND gate, OR gate, NOT gate, and XOR gate, each possessing unique characteristics and applications in digital design.

The AND gate determines the output based on the logic AND function, where the output is HIGH only when all of its inputs are HIGH.

The OR gate performs the logic OR function, generating a HIGH output if any of its inputs are HIGH.

The NOT gate is a single-input logic gate that produces the inverse of its input, resulting in a HIGH output for a LOW input and vice versa.

The XOR gate, or exclusive OR gate, produces a HIGH output only when there is an odd number of HIGH inputs.

Behavior within Verilog

In Verilog, these logic gates are implemented using Primitive Gates, predefined constructs that enable us to simulate the behavior of actual electronic gates. Verilog supports a wide range of library primitives to model various components, including logic gates.

By using the appropriate Verilog syntax, we can define the behavior of these primitive gates and their connections within our Verilog designs. This allows us to create complex digital systems by combining and interconnecting different logic gates.

By understanding the functionality of Primitive Gates and their behavior within Verilog, we gain the necessary foundation to design and simulate digital circuits effectively. The next section will introduce the concept of User-defined Modules, which further enhances the modularity and reusability of our Verilog code.

Introduction to User-defined Modules

In the realm of Verilog, user-defined modules hold paramount significance in the creation of complex digital systems. These modules allow us to encapsulate specific functionalities into reusable blocks of code, promoting modularity and efficiency in our designs.

When working with Verilog, understanding the concept of module instantiation is crucial. Module instantiation refers to the process of creating an instance of a user-defined module within a bigger design. This enables us to reuse the same module across multiple instances, promoting code reusability and enhancing development productivity.

Defining module ports is another essential aspect of working with user-defined modules. Module ports act as interfaces that enable communication between the module and other components in the design. Ports serve as input and output connections, allowing data to flow in and out of the module. By carefully defining these ports, we can establish precise communication channels, enabling seamless integration of the modules within the overall system.

In Verilog, hierarchical design plays a vital role in creating modular and scalable systems. Hierarchical design refers to the practice of designing systems using multiple layers of modules, each implementing a distinct functionality. This architectural approach enhances the readability, maintainability, and reusability of our designs, paving the way for efficient development and future enhancements.

Benefits of User-defined Modules

There are numerous benefits to utilizing user-defined modules in Verilog:

- Code Reusability: User-defined modules allow us to create reusable blocks of code, reducing development time and effort.

- Modularity: By encapsulating specific functionalities within modules, we can achieve a highly modular design, making the code easier to understand and maintain.

- Design Scalability: Hierarchical design using user-defined modules enables easy scalability of the overall system, allowing for future expansions and modifications.

- Enhanced Testing Capabilities: User-defined modules facilitate effective simulation and testing of individual components, ensuring the overall system functions as intended.

By harnessing the power of user-defined modules, Verilog designers can build robust, scalable, and efficient digital systems.

https://www.youtube.com/watch?v=7l7G_BzjFdI

| Module | Description |

|---|---|

| ALU | An Arithmetic Logic Unit (ALU) module performs arithmetic and logical operations on binary data. |

| Decoder | A Decoder module decodes binary inputs into multiple output lines based on specific conditions. |

| Multiplexer | A Multiplexer module selects one of multiple input lines and routes it to a single output line based on a select signal. |

Creating User-defined Modules

In Verilog, creating user-defined modules allows us to build complex digital systems with enhanced modularity and reusability. In this section, we will explore various techniques such as using procedural blocks, parameterized modules, and hierarchical design to create and customize our own modules.

Procedural blocks in Verilog provide a structured way to describe the behavior of our modules. By using procedural blocks such as always and initial, we can define the sequential and combinational logic of our modules, enabling us to create complex functionality.

Parameterized modules are another powerful feature in Verilog that allows us to create modules with customizable parameters. By defining parameters in our module declaration, we can easily adapt the module’s behavior and configuration. This flexibility enhances reusability and simplifies design modifications.

Additionally, utilizing hierarchical design principles enables us to create modules that are composed of smaller, interconnected modules. This modular approach enhances our code organization and readability, making it easier to debug and maintain.

Procedural Blocks

Procedural blocks in Verilog are used to describe the behavior of modules by specifying the sequential and combinational logic. They allow us to implement complex functionality within our modules.

Common types of procedural blocks:

always @*– Executes whenever any input to the block changes its valuealways @(posedge clk)– Executes only on the positive edge of the clock signalinitial– Executes once at the beginning of the simulation

By using these procedural blocks and appropriate Verilog syntax, we can create customized behavior for our modules based on the specific requirements of our design.

Parameterized Modules

Parameterized modules allow us to create flexible and reusable modules in Verilog. By defining parameters in our module declaration, we can customize the module’s behavior and configuration without modifying the module’s internal structure. Parameters can be used to set values, sizes, or even define different variations of the same module.

Example:

“`verilog

module Adder #(parameter WIDTH = 8) (input [WIDTH-1:0] a, b, output [WIDTH-1:0] sum);

// Implementation

endmodule

“`

Here, the Adder module is parameterized with a WIDTH parameter, allowing us to create adders of different data widths based on our requirements. This flexibility enhances modularity and simplifies design modifications.

Hierarchical Design

Hierarchical design is a key concept in Verilog that enables us to create complex digital systems by organizing modules in a hierarchical structure. It allows us to break down a system into smaller, interconnected modules for easier development and maintenance.

With hierarchical design, we can create modules that consist of instantiated sub-modules. This approach encourages code reuse, enhances scalability, and improves overall system understanding.

Example:

“`verilog

module CPU;

// Sub-modules instantiation

Adder adder_inst (.a(a), .b(b), .sum(sum));

// …

endmodule

“`

In the example above, the CPU module instantiates the Adder module as a sub-module, allowing us to reuse the Adder module within the CPU module.

By leveraging hierarchical design, we can create complex digital systems in Verilog with ease and maintainability.

Procedural Blocks vs. Parameterized Modules

| Procedural Blocks | Parameterized Modules |

|---|---|

| Used to describe behavior and logic | Allow customization of module behavior and configuration |

| Implement complex functionality | Enhance modularity and reusability |

Includes blocks like always and initial |

Enable customization with defined parameters |

In summary, creating user-defined modules in Verilog empowers us to design and implement complex digital systems effectively. By utilizing procedural blocks, parameterized modules, and hierarchical design, we can enhance the modularity, reusability, and flexibility of our Verilog code.

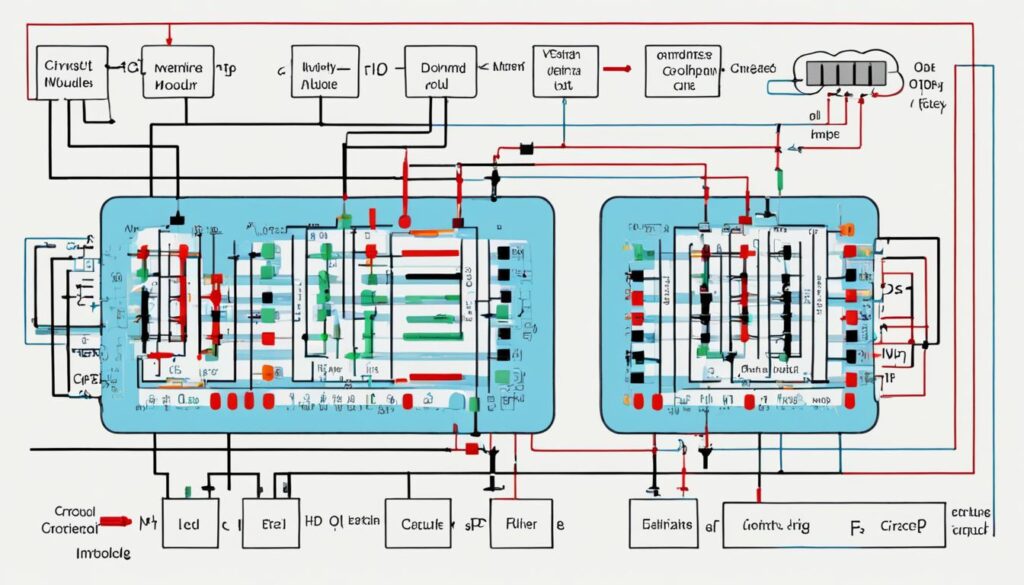

Interconnecting Modules

In the world of Verilog design, interconnecting modules is a crucial aspect that enables effective communication between different modules. By establishing connections between modules, we can create complex digital systems and ensure seamless data flow throughout the design. In this section, we will explore the concept of interconnecting modules and discuss key elements like Verilog wires, module connections, and dataflow modeling that facilitate this process.

Verilog Wires

A vital component in interconnecting modules is the use of Verilog wires. These wires serve as physical pathways for transferring data between modules. Think of them as the conductive links that allow information to flow from one module to another. By properly defining and connecting wires, we can establish the necessary connections to ensure smooth data exchange.

Module Connections

Module connections play a significant role in interconnecting modules effectively. When connecting modules, it is essential to identify the inputs and outputs of each module and establish the appropriate connections. This can be achieved by mapping the inputs and outputs of one module to the inputs and outputs of another module, ensuring that the data is transmitted accurately and efficiently.

In Verilog, module connections are typically specified in the module instantiation statement. By correctly defining and connecting the module ports, we can establish the necessary communication channels between modules, enabling them to work together harmoniously.

Dataflow Modeling

Dataflow modeling is a methodology that emphasizes the flow of data between different modules in a Verilog design. In this approach, the data is modeled as a stream that passes through various modules, with each module performing specific operations on the data. By implementing dataflow modeling techniques, we can effectively manage the interconnections between modules and ensure the correct flow of data throughout the design.

In dataflow modeling, the flow of data is controlled by the connections established between modules and the logic implemented within each module. By defining these connections and incorporating appropriate dataflow modeling techniques, we can create efficient and reliable Verilog designs.

To better understand the concept of interconnecting modules, let’s take a look at an example:

In the above diagram, we have two modules, Module A and Module B. The wires connecting the modules represent the intermodule connections, allowing the transfer of data between the modules. By properly defining the module ports and establishing the correct connections, we enable the modules to communicate and collaborate effectively.

Table: Example of Interconnected Modules

| Module A | Module B |

|---|---|

| Input A | Output B |

| Input B | Output C |

| Output X | Input D |

In the table above, we see the inputs and outputs of Module A and Module B, highlighting the connections between them. This representation provides a clear overview of how the modules are interconnected and the data flow between them.

By understanding the concepts of Verilog wires, module connections, and dataflow modeling, we can effectively interconnect modules in our Verilog designs. These interconnections enable the creation of complex and functional digital systems, allowing modules to work together harmoniously and achieve the desired behavior.

Conclusion

Throughout this article, we have explored the essential concepts of Primitive Gates and user-defined Modules in Verilog. We have gained a comprehensive understanding of how these building blocks contribute to the design and simulation of complex digital systems using Verilog HDL.

By grasping the fundamentals of Primitive Gates, including logic gates such as AND, OR, NOT, and XOR, we can effectively manipulate signals and create intricate digital circuits. Additionally, our understanding of user-defined Modules has allowed us to construct modular, reusable code, enabling hierarchical design and smooth interconnection between different components.

With the knowledge gained from this article, you are now equipped to embark on Verilog HDL design and simulation journeys confidently. Whether you are designing integrated circuits, processors, or complex digital systems, the understanding of Primitive Gates and user-defined Modules will serve as a solid foundation for your Verilog projects.