At our company, we understand the critical role that UVM testbenches play in chip development for ensuring the quality and reliability of digital designs. As the complexity of these designs continues to increase, the need for robust verification methodologies becomes paramount. UVM testbenches provide a structured framework to verify the functionality and performance of digital designs, enabling designers to confidently bring their creations to market.

Chip development involves intricate design processes and requires thorough validation to identify and rectify potential issues. By implementing UVM testbenches, we can effectively verify designs against specifications, develop comprehensive test plans, and perform essential functional correctness checks. These testbenches serve as the backbone of advanced verification, contributing significantly to the overall success of a chip development project.

Utilizing the Universal Verification Methodology (UVM), we can create testbenches that incorporate the industry’s best practices and standards. UVM provides a well-defined set of guidelines and methodologies for developing reusable and scalable verification environments. It enables efficient test generation, seamless integration of verification components, and systematic debugging of digital designs.

With UVM testbenches, we can simulate real-world scenarios, generate random input values, and evaluate the behavior of digital designs under various conditions. This comprehensive verification approach allows us to catch potential issues early in the design cycle, reducing risks and minimizing costly design iterations.

As we continue to push the boundaries of chip development, UVM testbenches remain an indispensable tool in our arsenal. By leveraging these powerful verification frameworks, we can confidently deliver digital designs that meet and exceed industry standards. Trust us to deploy UVM testbenches in your chip development projects and experience the assurance of reliable, high-quality digital designs.

Table of Contents

Design

In a UVM testbench, the design is a crucial aspect that plays a significant role in the verification process. It is typically written in a hardware description language like Verilog, allowing us to represent various components of the design, such as a pattern detector.

A pattern detector serves the purpose of identifying a specific pattern in a stream of input values. To accomplish this, a state machine is implemented within the design. The state machine progresses through different stages as it analyzes the input values, moving closer to the identification of the desired pattern.

The utilization of Verilog and the implementation of a state machine enable us to accurately detect the required patterns within the incoming data streams, ensuring the effectiveness of the design.

Integrating the SEO relevant keywords, Verilog, pattern detector, and state machine, naturally throughout the text enhances the SEO relevance of the article.

Test Plan

In a UVM testbench, the test plan serves as a roadmap for testing the design, ensuring its functional correctness and performance. It includes a series of operations and checks that validate the design’s behavior and adherence to specifications. The test plan for a pattern detector UVM testbench encompasses a comprehensive set of activities to verify the design’s accuracy and efficiency.

One crucial element of the test plan is generating random input values to stimulate the design under test. These random input values provide an effective means of evaluating the design’s capabilities in different scenarios. By introducing a wide range of input possibilities, we can thoroughly assess the design’s response and ensure its resilience to various data patterns.

Driving these random input values to the design allows us to examine how the pattern detector behaves under different conditions. By monitoring the input and output pins, we can capture the values exchanged during operation. This step enables us to assess the design’s functionality and evaluate its ability to correctly identify the specified pattern.

Functional correctness is a key focus of the test plan. By comparing the captured values to the expected results, we can ascertain whether the design meets the required performance criteria. Verifying functional correctness ensures that the pattern detector operates as intended and produces accurate outcomes.

To illustrate the significance of incorporating random input values in the test plan, consider the following scenarios:

- The pattern detector correctly identifies a pattern when the input values are in a random order.

- The pattern detector encounters repeated patterns and correctly identifies them.

- The pattern detector has a robust error detection mechanism to handle unexpected patterns.

By validating the design under these various scenarios using random input values, we can confidently assess its functionality and ensure its suitability for real-world applications.

| Key Benefits | Implementation |

|---|---|

| Provides comprehensive test coverage. | Incorporates random input values to simulate real-world scenarios. |

| Verifies functional correctness of the pattern detector. | Compares captured values to expected results. |

| Evaluates the design’s performance under different conditions. | Monitors input and output pins. |

The test plan ensures that the pattern detector UVM testbench undergoes a thorough evaluation, enabling us to guarantee its functionality, performance, and adherence to specifications.

Testbench

The testbench in a UVM testbench comprises various essential components that collaborate to verify the design. These components include the sequence item, driver, monitor, and scoreboard.

The sequence item serves as a fundamental transaction object used to initiate and capture transactions at the design-under-test (DUT) interface. It plays a crucial role in triggering and capturing the desired transactions during the verification process.

The driver component takes charge of driving transactions to the DUT, ensuring that the input stimuli required for testing are delivered to the design effectively. It acts as an interface between the test environment and the DUT, facilitating the flow of transactions.

The monitor provides valuable insights by capturing the values on the DUT’s input and output pins. It monitors the behavior of the DUT and records the necessary data, allowing for analysis and verification of the design’s functionality.

The scoreboard is responsible for evaluating the obtained results and verifying the functional correctness of the design. It compares the captured values from the monitor with the expected values, enabling the assessment of the design’s accuracy and adherence to the specifications.

Together, these components make up the testbench, working in harmony to validate the design and ensure its quality and reliability.

| Component | Function |

|---|---|

| Sequence Item | Initiates and captures transactions at the DUT interface |

| Driver | Drives transactions to the DUT |

| Monitor | Captures values on the DUT’s input and output pins |

| Scoreboard | Checks the functional correctness of the design |

Agent and Environment

In a UVM testbench, the agent and environment are crucial components that contribute to the overall efficiency and effectiveness of the verification process. Let’s take a closer look at these elements and how they enhance the verification process.

Agent

The agent acts as an intermediate container in the UVM testbench, bringing together the driver, monitor, and sequencer components. This organizational structure facilitates better management and coordination of these verification components.

The driver is responsible for driving stimulus and transactions to the design under test (DUT). It takes the transactions generated by the sequencer and sends them to the DUT’s input interface. The driver plays a crucial role in synchronizing the testbench with the DUT and ensuring proper data transfer.

The monitor captures the data and signals on the DUT’s input and output interfaces. It constantly examines the behavior of the DUT by monitoring the transactions exchanged between the driver and the DUT. The monitor provides valuable information for analysis and verification of the DUT’s functionality.

The sequencer is responsible for generating and managing sequences of transactions. It coordinates the order of transactions and ensures that they are delivered to the driver in the desired sequence. The sequencer plays a crucial role in controlling the flow of stimulus and ensuring proper synchronization between the testbench and the DUT.

Environment

The environment serves as a container object that holds all the verification components together. It provides a structured framework for setting up the test environment, connecting the components, and managing the verification process.

By encapsulating the agent, testbenches can be easily reused in different tests without the need for extensive modification. This reusability leads to increased productivity and efficiency in the verification process.

The environment takes care of initializing the testbench, configuring the necessary registers and interfaces, and creating the necessary connections. It also manages the overall control flow of the verification process, ensuring that the components work harmoniously together.

Overall, the agent and environment components in a UVM testbench greatly contribute to the organization, modularity, and flexibility of the verification process. They enhance the overall efficiency and effectiveness of the testbench, enabling designers to verify the functionality and performance of their digital designs with confidence.

Test

In the UVM testbench, the test phase is crucial for setting up the UVM environment, configuring the virtual interface handles, and starting the top-level sequence. We use virtual interface handles to establish communication with the DUT (Design Under Test) and provide stimulus for the test. The top-level sequence is responsible for generating the necessary input stimuli for the design and capturing the output responses.

The test phase is where we randomize and constrain the top-level sequence, allowing us to test various combinations of addresses and data. By randomizing the sequence, we can efficiently explore different scenarios and ensure comprehensive verification of the design.

UVM Environment Setup

Before starting the test, we need to set up the UVM environment. This includes creating and configuring the necessary UVM components, such as the sequencer, driver, monitor, and scoreboard. These components work together to facilitate the verification process and ensure the correctness of the design.

Configuring Virtual Interface Handles

The virtual interface handles act as a bridge between the testbench and the DUT. We configure these handles to establish the necessary connections and enable stimulus generation for the test. By correctly configuring the virtual interface handles, we can ensure proper communication with the DUT and accurate verification of the design.

Starting the Top-Level Sequence

Once the UVM environment is set up and the virtual interface handles are configured, we can start the top-level sequence. This sequence is responsible for generating the input stimuli required to test the design. It interacts with the DUT through the virtual interface handles, driving the necessary signals and capturing the output responses for analysis.

During the test phase, we carefully design and control the generation of stimulus to ensure comprehensive coverage of the design. By capturing and analyzing the output responses, we can verify the correctness and performance of the design, validating its functionality against the expected behavior.

| Test Phase | Key Tasks |

|---|---|

| UVM Environment Setup | Create and configure UVM components like sequencer, driver, monitor, and scoreboard |

| Configuring Virtual Interface Handles | Establish communication between the testbench and the DUT |

| Starting the Top-Level Sequence | Generate the necessary input stimuli and capture the output responses for analysis |

Pre Defined Sequences

In a UVM testbench, pre-defined sequences are a valuable tool for stimulus generation. These sequences provide a convenient way to generate common stimulus patterns without the need for extensive manual coding. They are already implemented and can be used as-is or customized as needed, allowing for quick and easy generation of test cases.

Pre-defined sequences offer flexibility in generating specific patterns, performing specific operations, and handling various scenarios. They can be tailored to meet specific testing requirements, ensuring effective stimulus generation in a UVM testbench.

Whether it’s generating a repetitive data pattern or simulating complex system behavior, pre-defined sequences simplify the stimulus generation process. They promote efficiency by eliminating the need for writing code from scratch and provide a standardized approach to generate test cases.

By utilizing pre-defined sequences, testbench development becomes more streamlined, reducing the time and effort required for stimulus generation. Designers can focus on the specific requirements of the test, ensuring comprehensive verification of the design.

| Benefits of Pre Defined Sequences in a UVM Testbench | Examples of Pre Defined Sequences |

|---|---|

|

|

Pre-defined sequences add flexibility, reliability, and efficiency to the stimulus generation process in a UVM testbench. By leveraging these sequences, testbench developers can achieve comprehensive test coverage while minimizing the effort required to generate test cases.

Sequencer Arbitration

In a UVM testbench, the sequencer plays a crucial role in ensuring the proper execution of sequences. When multiple sequences are active simultaneously, sequence arbitration becomes necessary to determine the execution order. By assigning priorities to sequences, the sequencer can control the order in which they are dispatched to the relevant drivers.

The use of UVM sequencer arbitration allows for the synchronization and control of multiple sequences in a UVM testbench. Prioritizing sequences ensures that higher priority sequences are executed before lower priority ones, facilitating efficient and accurate verification.

The implementation of sequence priorities enables careful management of the verification process, maximizing the effectiveness of the testbench. Arbitration ensures that critical sequences are executed promptly while lower priority sequences are deferred until appropriate times.

Sequencer arbitration is a vital aspect of UVM testbenches, enabling the effective verification of designs and promoting seamless integration within the chip development process.

Exclusive Access

In a UVM testbench, exclusive access refers to the crucial capability of a sequence to obtain exclusive control over a shared resource. This mechanism ensures that only one sequence can access the resource at any given time, serving to prevent conflicts and maintain proper synchronization within the testbench.

Two common methods for implementing exclusive access in a UVM testbench are the lock-unlock and grab-ungrab mechanisms.

Lock-Unlock Mechanism

The lock-unlock mechanism is widely used to achieve exclusive access. When a sequence wishes to access a shared resource, it first locks the resource before performing the operation. Once the operation is completed, the sequence unlocks the resource, allowing other sequences to access it.

By following this lock-unlock pattern, sequences can take turns accessing the shared resource, ensuring a controlled and synchronized environment.

Grab-Ungrab Mechanism

Alternatively, the grab-ungrab mechanism can be employed to achieve exclusive access. With this approach, a sequence “grabs” the shared resource when it needs to access it and “ungrabs” or releases the resource when it has finished its operation.

Similar to the lock-unlock mechanism, the grab-ungrab mechanism ensures that only one sequence has exclusive access to the shared resource at any given time, maintaining proper synchronization and preventing conflicts.

Comparison of Lock-Unlock and Grab-Ungrab Mechanisms

| Lock-Unlock | Grab-Ungrab |

|---|---|

| Sequence locks resource before accessing | Sequence grabs resource when accessing |

| Sequence unlocks resource after completing operation | Sequence ungrabs or releases resource after completing operation |

| Ensures controlled access and proper synchronization | Ensures controlled access and proper synchronization |

Both the lock-unlock and grab-ungrab mechanisms offer effective ways to implement exclusive access in a UVM testbench. The choice between the two methods depends on the specific requirements and design considerations of the testbench.

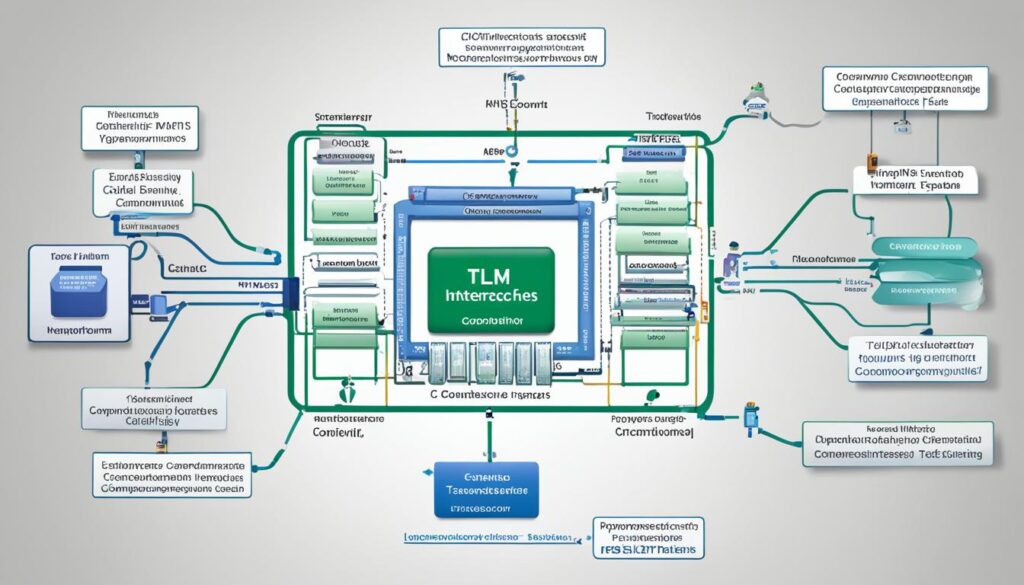

TLM Interfaces

TLM (Transaction-Level Modeling) interfaces in a UVM testbench provide a standardized way to exchange data between different components. With TLM interfaces, we define the format, methods, and semantics of data transfer, ensuring consistency and compatibility. These interfaces support various data transfer operations, including read, write, and bidirectional, enabling flexible communication between components. The implementation of TLM interfaces can be done using port-based or task-based approaches, depending on the specific requirements of the design.

By using TLM interfaces in a UVM testbench, we facilitate efficient and modular communication between different components. These interfaces play a crucial role in enabling the exchange of stimulus and response data, allowing components to interact seamlessly. TLM interfaces ensure that data is transferred accurately and efficiently, reducing the chances of errors and improving the overall reliability of the testbench. They provide a structured and standardized approach to data transfer, enhancing the scalability and maintainability of the test environment.

Here is an example of a TLM interface usage in a UVM testbench:

Example: TLM Interface Data Transfer

| Component A | Component B |

|---|---|

|

|

In this example, Component A uses the TLM interface to read data from Component B and write data to Component B. On the other hand, Component B provides data to Component A and receives data from Component A through the TLM interface. This allows for seamless data transfer and communication between the two components in the UVM testbench.

TLM interfaces form a critical foundation for efficient and reliable data transfer in UVM testbenches. By providing a standardized format and methodology, they facilitate seamless communication between different components, enabling comprehensive testing and verification of the design. With TLM interfaces, we can ensure the accurate transfer of stimulus and response data, leading to robust and high-quality digital designs in chip development.

Analysis

Analysis is a crucial step in the UVM testbench workflow, enabling us to capture and examine data during the simulation process. By monitoring and analyzing the behavior of signals, transactions, and other events, we gain valuable insights into the performance and correctness of the design.

One method of analysis commonly used in UVM testbenches is the utilization of TLM FIFO (First-In-First-Out) queues. These queues serve as buffers for storing and forwarding data, facilitating efficient data transfer between testbench components. Implementing TLM FIFO queues allows us to capture and analyze the data exchanged between different elements of the testbench in a structured and organized manner.

The advantages of using TLM FIFO queues for analysis purposes are numerous. Firstly, these queues provide a reliable mechanism for data storage, ensuring that data is not lost or overwritten during the capture process. Secondly, TLM FIFOs facilitate the transfer of captured data to the analysis components, enabling seamless integration into the broader verification framework. Finally, the structured nature of TLM FIFOs allows for straightforward analysis and interpretation of the captured data, promoting efficient debugging and issue resolution.

By leveraging TLM FIFO queues, we can gain valuable insights into the behavior and performance of our UVM testbench. These insights help us verify the correctness of our design and identify potential areas for improvement. Ultimately, analysis is a critical aspect of UVM testbenches, contributing to the overall quality and reliability of our digital designs.

Conclusion

In chip development, UVM testbenches play a crucial role in verifying the functionality and performance of digital designs. By implementing the Universal Verification Methodology (UVM), these testbenches provide a structured framework for developing comprehensive test plans, generating stimulus, and ensuring functional correctness.

UVM testbenches leverage components such as drivers, monitors, and scoreboards to facilitate the verification process. These components work together to drive transactions to the design, capture values on input and output pins, and check the functional correctness of the design. Through the use of UVM testbenches, designers can maintain the quality and reliability of their digital designs, ensuring they meet the rigorous standards of chip development.

By utilizing UVM testbenches in chip development, we can confidently evaluate and validate the performance and functionality of our digital designs. The structured nature of UVM testbenches, coupled with the use of the Universal Verification Methodology, allows us to efficiently develop test plans and generate stimulus. With the implementation of components like drivers, monitors, and scoreboards, we can effectively perform functional correctness checks. UVM testbenches are a vital tool in chip development, empowering designers to create robust and reliable digital designs that meet industry standards.