Welcome to our comprehensive guide on Karnaugh maps, an indispensable tool in the realm of digital logic design. In this first section, our focus is to unravel the concept and the critical role that K-maps play in the simplification of complex logical expressions. We will delve into the origins of Karnaugh maps, elucidate their historical significance, and draw a clear picture of their structural composition. As specialists in digital logic design, we recognize the transformative power K-maps hold in optimizing circuitry—a testament to their enduring relevance and utility in the field.

By engaging with our step-by-step process, you will garner practical knowledge that extends far beyond theoretical constructs. Karnaugh maps serve as a visual and intuitive method for minimizing Boolean algebra expressions, enabling you to design and troubleshoot digital circuits with enhanced precision and efficiency. Whether you are a seasoned engineer or an aspiring student, our insights into K-maps will equip you with the prowess to tackle increasingly complex digital challenges with confidence.

Table of Contents

Introducing Karnaugh Maps for Boolean Algebra

As we navigate through the fascinating landscape of digital logic design, we encounter a pivotal tool—Karnaugh maps. These maps are not merely diagrams but guides that reveal the elegance of Boolean algebra. Garnering historical significance with their origins rooted in the work of Maurice Karnaugh in 1953, Karnaugh maps have stood the test of time in simplifying digital circuits. Before we delve deeper into their usage, let us pay homage to its origins and appreciate the intricacy of its structure.

Origins and Historical Significance of K-maps

The journey of Karnaugh maps began as an evolution from Veitch charts and Marquand diagrams. Pioneered by Maurice Karnaugh, these maps marked a significant leap in the visualization of Boolean algebra. Their use in digital circuits underscores a historical transformation in logic design, offering a methodical approach to reduce Boolean expressions to their simplest forms. This development, emblematic of innovation, paved the way for the streamlined and efficient circuit designs we rely on today.

Understanding the Basic Structure of a K-map

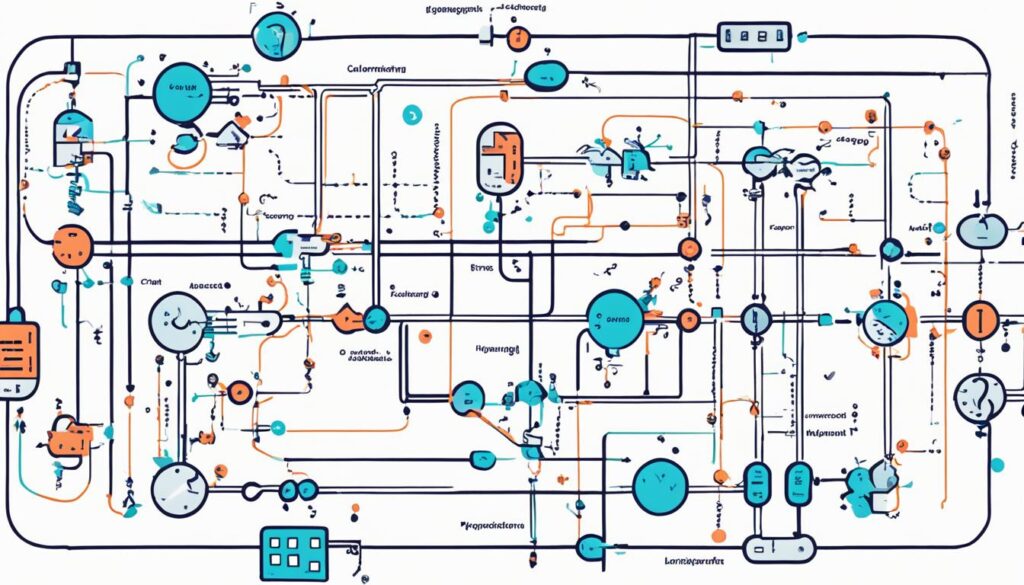

The structure of a Karnaugh map is distinctive, setting it apart from a conventional truth table. A K-map is composed of a grid of squares, each representing a unique variable combination in Boolean algebra. This grid format allows for a visual grouping of terms—significantly simplifying the logic minimization process. By eliminating the redundancy prevalent in truth tables, Karnaugh maps gift us with a clearer and more immediate path to logic simplification. Their significance in digital circuits cannot be overstated.

Significance in Simplifying Digital Circuits

Karnaugh maps hold immense value in digital logic because they are quintessential in simplifying digital circuits. As a tool, they facilitate the identification of redundant operations within Boolean expressions, allowing for circuit simplifications that result in fewer components and increased reliability. Through strategic groupings and the elimination of superfluous gates, Karnaugh maps ensure that innovations in digital circuitry continue to thrive on principles of efficiency and elegance.

In this expansive realm of Boolean algebra, the Karnaugh map stands as a testament to our progress in digital logic design. With the origins and structure of these maps in mind, let us continue to peel back the layers, uncovering their full potential in simplifying complex digital circuits.

Breaking Down Karnaugh Maps

In our exploration of Karnaugh maps, we delve into the intricacies of their structure, ensuring a deeper comprehension of how this tool greatly assists in the simplification of boolean expressions. By breaking down the Karnaugh maps into their elemental components, we reveal the underpinning logic that facilitates a streamlined method for Boolean problem-solving.

At the core of Karnaugh maps, we find individual cells, each representing a unique combination of input conditions. These cells are the basic building blocks of the Karnaugh maps, arranged in a grid-like structure that visually aids in the simplification process.

Grouping is a pivotal concept in the utilization of Karnaugh maps, wherein we identify the most efficient collections of adjacent cells containing 1s (or 0s). This process of grouping related terms drastically reduces the complexity of Boolean algebra expressions.

| Input Variables | Individual Cells | Optimal Grouping Examples |

|---|---|---|

| AB | 00, 01, 10, 11 | Group of four cells denoting (A+B’) |

| ABC | 000, 001, …, 111 | Group of two cells revealing B’ (when A and C are don’t cares) |

| ABCD | 0000, 0001, …, 1111 | Eights group simplifying to A’ (B, C, D are don’t cares) |

It is not just about the identification of these groupings but also about knowing the rule set for optimal grouping: groups must be of sizes 2^n, they can be formed horizontally or vertically but not diagonally, and wrapping around the edges is accepted. Mastery of these details ensures that we can maximize the functionality of Karnaugh maps in breaking down and simplifying complex Boolean algebra expressions.

The Step-by-Step Process of Using Karnaugh Maps

Mastering Karnaugh maps is a fundamental skill for any professional involved in digital logic design. Our guide will take you through a streamlined step-by-step process to ensure that you efficiently use Karnaugh maps for simplification of boolean expressions.

Selecting the Correct K-map Layout for Variables

Firstly, selecting the appropriate layout for your Karnaugh map is crucial. The number of variables you’re working with will determine the size of the map. Typical layouts range from two to six variables. For instance, a three-variable function will require a 2×4 K-map, as each variable doubles the number of rows or columns.

- 2 Variables – 2×2 layout

- 3 Variables – 2×4 layout

- 4 Variables – 4×4 layout

- 5 Variables – 5-variable K-maps are a bit more intricate, often requiring two 4×4 maps to represent all possible combinations.

By selecting the layout that corresponds to your variables, you set the stage for accurate grouping and, ultimately, the correct simplification of your boolean expression.

Placing Minterms and Maxterms in the K-map

The next step involves placing minterms (for SOP – Sum of Products) and maxterms (for POS – Product of Sums) within the Karnaugh map. Minterms correspond to the ‘1’ values in your truth table while maxterms align with ‘0’ values.

- Identify all minterms or maxterms from the truth table or boolean expression.

- Place a ‘1’ for each minterm and a ‘0’ for each maxterm into their respective cells based on combinations of variables.

Ensuring accuracy in this stage is pivotal in the simplification process, as it directly influences the grouping phase.

Grouping in K-maps for Simplification

Grouping is where the Karnaugh maps’ ability to simplify boolean expressions shines. It’s about finding clusters of ‘1’s for minterms or ‘0’s for maxterms in adjacent cells. Each group must contain a power of 2 numbers of cells (1, 2, 4, 8, etc.)

| Group Size | Number of Variables Eliminated |

|---|---|

| Single cell (1) | None – Represents a full product term |

| Pair of cells (2) | One variable eliminated |

| Quartet of cells (4) | Two variables eliminated |

| Octet of cells (8) | Three variables eliminated |

After grouping, each cluster is used to form part of the simplified expression. For instance, if all ‘1’s in a group coincide on a variable being true or false, that variable can be eliminated from the product term for that group.

Combining all these steps – selecting the right layout, placing minterms or maxterms, and effective grouping – we achieve simplification through Karnaugh maps, enhancing the efficiency of logic circuit designs.

Real-World Applications of Karnaugh Maps

Through our exploration of Karnaugh maps and their applications, we’ve discovered the profound impact they have had on logic circuit design and the optimization of electronic devices. These tools are not merely academic exercises; they are utilized in diverse sectors to enhance the efficiency and functionality of digital systems. In real-world scenarios, the advantages of applying Karnaugh maps to circuit optimization can be seen in streamlined production processes, cost reductions in electronics manufacturing, and the development of cutting-edge technology.

In industries where electronic devices are pivotal, Karnaugh maps serve as an essential instrument for electrical engineers. Their capacity to simplify complex logic circuits translates to real-world applications that span from consumer electronics to advanced computational systems. By reducing the number of logic gates necessary in a circuit, these tools assist engineers in creating more compact and efficient designs—a key requirement in the miniaturization trend of technology products.

| Industry | Application of Karnaugh Maps | Impact on Circuit Optimization |

|---|---|---|

| Consumer Electronics | Simplification of logic for user interfaces | Reduced component count and improved device reliability |

| Automotive | Streamlining control systems for vehicles | Higher performance with lower power consumption |

| Telecommunications | Efficient signal processing circuits | Faster data transmission with reduced error rates |

| Computing Hardware | Optimization of microprocessor logic units | Enhanced processing speeds with smaller chip area |

The application of Karnaugh maps extends well beyond traditional computing and electronics. In the burgeoning field of artificial intelligence, for instance, they facilitate the design of complex logic that underpins machine learning algorithms and neural networks, marking a significant step towards more intelligent and autodidactic systems. The power of Karnaugh maps to tackle intricate problems in logic circuit design ultimately powers the innovation and advancements we witness across a spectrum of technological frontiers.

- Assessing the impact of Karnaugh maps in the design and optimization of consumer electronic devices.

- Evaluating the efficiency improvements in automotive control systems achieved through Karnaugh maps.

- Analyzing the role of Karnaugh maps in advancing telecommunications infrastructure.

- Exploring the applications of Karnaugh maps in computing hardware to push the boundaries of processing capabilities.

As we navigate the complexities of modern electronic design, Karnaugh maps continue to play a pivotal role in circuit optimization, demonstrating their enduring value and potential. From the smartphones in our pockets to the cars we drive and the servers that form the backbone of the internet, the influence of Karnaugh maps is intricately woven into the fabric of our electronic world.

Advanced Techniques: Simplifying Complex Boolean Expressions

The landscape of digital logic design is continuously evolving, and as we tackle more intricate scenarios, the simplicity and efficiency of Karnaugh maps remain indispensable tools. We now advance our methodologies to manage complex boolean expressions, particularly when employing five variable K-maps. The challenges associated with such high-dimensional Karnaugh maps beckon for advanced techniques that we have perfected to streamline your design process.

Handling Five Variable K-Maps

In addressing five variable K-maps, it becomes evident that traditional methodologies can fall short. We navigate this complexity by segmenting the K-map into more manageable parts. Imagine this as dividing a daunting task into smaller, actionable steps. Our strategy focuses on grouping these variables effectively to visualize and simplify the expression. Below is a practical demonstration of minimizing a five variable boolean function using a Karnaugh map.

Given a logical expression with variables A, B, C, D, and E, we layout a five variable K-map, with 32 cells representing all possible combinations. Our mission is to target groups of 1s that can be powerfully minimized. To illustrate:

| Variables | Minterm Groupings | Reduced Expression |

|---|---|---|

| A, B, C, D, E | ABCDEFGH | A’B + AC’D’ |

| A, B, C, D, ~E | IJKLMN | B’D’E + A’C’ED |

Navigating “Don’t Cares” in Expression Minimization

Often in the design of logical circuits, we encounter scenarios where certain output conditions are inconsequential, referred to as “don’t cares.” Including these in our Karnaugh maps provides versatility in our approach to expression minimization, turning potential ambiguities into a potent simplification ally.

With “don’t cares,” we allow for these cells to be either 0 or 1, whichever benefits the simplification most. Here’s how we might utilize “don’t cares” in a boolean expression:

- We identify the “don’t care” cells and note their positions in the K-map.

- Depending on whether we aim to find the Sum of Products (SOP) or Product of Sums (POS), “don’t cares” are treated as 1s or 0s, respectively, to maximize groupings.

- We reassess the map with these flexibilities in mind, extending our groups to encompass these cells and thereby simplifying the overall expression.

By mastering these advanced techniques, we confidently embrace the complexities of digital logic design. Karnaugh maps serve as a cornerstone for our expertise in expression minimization, and we look forward to pushing the boundaries of efficiency and simplicity further together.

Conclusion

As we reach the end of our in-depth exploration, it is clear that the significance of Karnaugh maps in the realm of digital logic design cannot be overstated. These efficient tools have been at the forefront of simplification, enabling designers to convert complex boolean expressions into manageable and optimized circuits. Throughout this article, we have traced the evolution of Karnaugh maps, from their historical origins to their practical applications in today’s advanced electronic systems.

With each section, we sought to unpack the nuances of Karnaugh maps, illustrating their integral role in creating systems that embody both sophistication and efficiency. Our discussions highlighted the conducive role of Karnaugh maps in streamlining digital circuits, offering a beacon for both burgeoning and seasoned engineers striving to enhance circuit efficiency. The intricacies of managing variables and “don’t cares,” down to mastering the grouping of cells for minimized expressions, were all pivotal lessons shared within our summaries.

In conclusion, the journey with Karnaugh maps does not terminate here. We urge our readers to apply the methodologies and insights gleaned from our article to their own dynamic projects. The landscape of digital logic design is ever-evolving, and futher advancements beckon. May your pursuit of technical excellence be guided by the principles of simplification and efficiency that Karnaugh maps exemplify. Venture forward, harness these instrumental techniques, and let the precision of your logic designs be a testament to the power of knowledge applied with intention and prowess.