Welcome to our article on UVM Analysis Ports! In today’s fast-paced verification environments, effective communication and data analysis are crucial for ensuring the reliability and functionality of designs. That’s where UVM analysis ports come in.

UVM analysis ports are specialized TLM-based classes that play a key role in verification environments. They enable components to generate a stream of transactions, regardless of whether there is a target connected to it. This flexibility allows for efficient testbench data analysis and enhances the overall robustness of the verification process.

By leveraging the power of UVM analysis ports, engineers can create versatile verification environments that enable seamless communication and collaboration between components. Verification environments that incorporate these analysis ports provide valuable insights and facilitate effective analysis of testbench data.

In the following sections, we will explore the role of UVM analysis ports in component communication, the process of declaring and connecting these ports, best practices for their implementation, and the benefits they bring to verification environments. We will also provide examples of how UVM analysis ports can be leveraged for broadcasting transactions and coverage collection. Along the way, we’ll share some best practices to optimize the usage of these ports.

So, join us on this journey as we dive deeper into the world of UVM Analysis Ports!

Table of Contents

The Role of UVM Analysis Ports

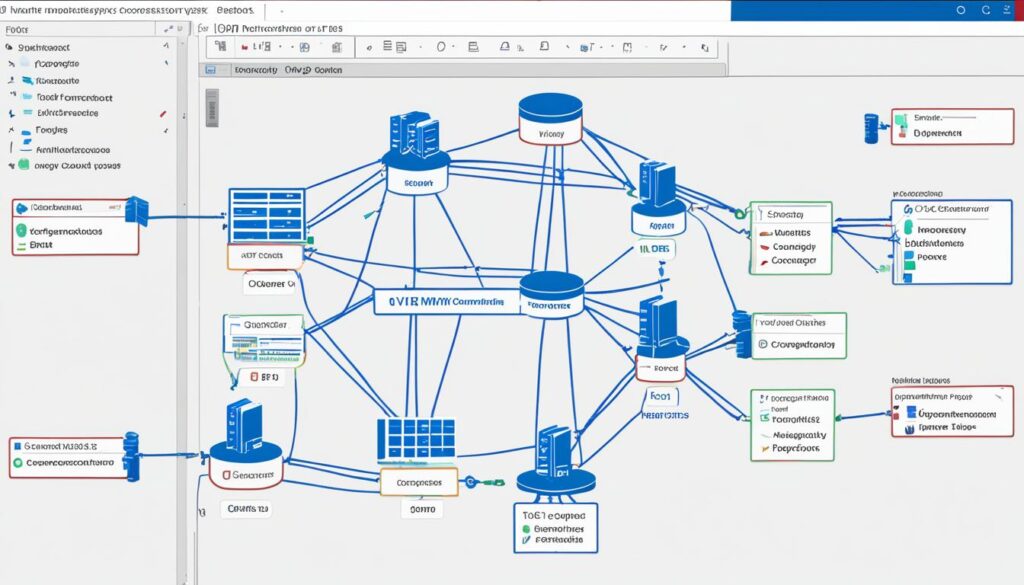

In a verification environment, UVM analysis ports play a crucial role in enabling efficient communication and data exchange between different components. Whether it’s a monitor or any other component, a UVM analysis port allows the generation of a stream of transactions, even if there is no connected target. This versatility empowers engineers to build highly flexible and modular verification environments. Let’s explore the role of UVM analysis ports in component communication and data broadcasting.

An analysis port can be connected to zero, one, or multiple analysis exports, which are in turn connected to other components. By invoking the write() method of the analysis port, a component can cascade through its connected exports, invoking the write() method of each export. This mechanism facilitates data broadcasting, allowing multiple components to receive and process the same transaction simultaneously.

By leveraging UVM analysis ports, components can communicate efficiently and effectively in a verification environment. The ability to generate a stream of transactions without being dependent on connected targets promotes modularity and reusability. Engineers can easily connect and disconnect components from analysis ports, enabling flexible system composition and promoting collaborative analysis across various parts of the verification environment.

With the power of UVM analysis ports, engineers can build robust verification environments that facilitate seamless communication and data exchange. The role of UVM analysis ports extends beyond individual components, enabling efficient analysis and collaborative testing on a system-wide level.

Benefits of UVM Analysis Ports in Component Communication:

- Promote modularity and reusability in the verification environment

- Facilitate efficient data broadcasting among components

- Enable flexible system composition and collaborative analysis

| Role of UVM Analysis Ports | Component Communication | Data Broadcasting |

|---|---|---|

| Promote modularity and reusability | Allow components to interact without direct connections | Enable multiple components to receive and process the same transaction |

| Flexible system composition | Communication between different parts of the verification environment | Promote collaborative analysis |

Declaring and Connecting UVM Analysis Ports

When working with UVM analysis ports, the first step is to declare them within the desired component. To do this, we need to define an instance of the uvm_analysis_port class. This analysis port can be embedded within any component in the verification environment. Its interface consists of a single function, write(), which is responsible for sending transactions from the component to the connected analysis exports.

To establish the connection between the analysis port and the analysis exports, we use the connect() method. This method allows us to connect the analysis port to zero, one, or many analysis exports. By establishing this connection, we create a communication channel, also known as a TLM channel, between the component and the connected exports. This channel enables efficient data exchange and facilitates collaborative analysis between different parts of the verification environment.

Declaring UVM Analysis Ports

To declare an analysis port, we define an instance of the uvm_analysis_port class within the desired component. This can be done within the body of the parent component class or in any lower-level module or interface.

“`verilog

class MyComponent extends uvm_component;

uvm_analysis_port#(MyTransaction) analysis_port;

endclass

“`

In the example above, we declare an analysis port named analysis_port of type uvm_analysis_port with the template parameter MyTransaction. This analysis port can be used to send transactions of type MyTransaction from the component to the connected analysis exports.

Connecting Analysis Ports

To connect the analysis port to analysis exports, we use the connect() method. This method establishes the connection between the analysis port and the analysis exports, enabling data exchange between components.

“`verilog

class MyComponent extends uvm_component;

uvm_analysis_port#(MyTransaction) analysis_port;

function void build_phase(uvm_phase phase);

super.build_phase(phase);

MyAnalysisExport exp1 = new();

MyAnalysisExport exp2 = new();

analysis_port.connect(exp1);

analysis_port.connect(exp2);

endfunction

endclass

“`

In the above example, we have a component named MyComponent with an analysis port analysis_port. Inside the build_phase() method, we create two analysis exports, exp1 and exp2. We then connect both of these analysis exports to the analysis port using the connect() method.

By connecting the analysis port to the analysis exports, we establish a communication channel between the component and the connected exports. This allows the component to send transactions through the analysis port to be processed by the analysis exports.

Overall, the process of declaring and connecting UVM analysis ports is an essential aspect of building a robust and efficient verification environment. By following these practices, we can enable effective communication and data exchange between components while maintaining modularity and reusability. With UVM analysis ports, we can enhance our verification process and gain valuable insights into the behavior of our designs.

Implementing Analysis Ports and Exports

When it comes to implementing analysis ports and exports in UVM, the process involves creating an instance of the uvm_analysis_port class and connecting it to the analysis exports. The analysis exports, on the other hand, are implemented using the uvm_analysis_imp class. These components work together to facilitate efficient transaction processing in a verification environment.

The first step in implementing an analysis port is to create an instance of the uvm_analysis_port class within the desired component. This establishes a communication channel through which the component can send transactions to connected analysis exports. The uvm_analysis_port interface consists of a single function, the write() method. This method is responsible for invoking the write() method of each connected analysis export.

To implement the analysis exports, the uvm_analysis_imp class is used. This class defines the behavior of the connected component when it receives a transaction from an analysis port. It contains the write() method that can be customized to process the received transaction according to the requirements of the component. By implementing this method, engineers can define the desired behavior for each connected analysis export.

Through the implementation of analysis ports and exports, the verification environment gains the capability to process transactions efficiently. When a component calls the write() method of the analysis port, it triggers the write() method of each connected analysis export. This enables seamless transaction processing and enables components to collaborate effectively in analyzing testbench data.

Connecting Multiple Analysis Ports and Exports

When designing a verification environment, it is often necessary to establish connections between multiple analysis ports and exports. This allows for enhanced component connectivity and efficient data exchange between different parts of the system. By leveraging the capabilities of multiple analysis ports and exports, engineers can facilitate collaborative analysis and ensure the seamless flow of transaction data.

Connecting multiple analysis ports to a single analysis export is a common practice in verification environments. This allows for concurrent data transfer from different components to a centralized destination. For example, multiple monitors can send transaction data simultaneously to a single analysis export, enabling comprehensive analysis and reporting.

On the other hand, connecting multiple analysis exports to a single analysis port offers the flexibility to distribute transaction data across various components. This enables parallel processing and allows multiple components to independently analyze and respond to the received transactions.

The establishment of these connections enhances component connectivity and promotes efficient data exchange. It enables components to collaboratively analyze the testbench data and ensures that the right information reaches the right components.

| Analysis Ports | Analysis Exports |

|---|---|

| Component A | Export 1 |

| Component B | Export 1 |

| Component C | Export 1 |

| Component D | Export 1 |

| Component E | Export 2 |

| Component F | Export 2 |

As shown in the table above, multiple analysis ports (Component A, B, C, and D) are connected to a single analysis export (Export 1). Additionally, Component E and F are connected to Export 2. This configuration allows for efficient communication and data exchange between the components.

By leveraging multiple analysis ports and exports, engineers can build highly interconnected verification environments that enable comprehensive analysis and robust verification. The flexibility provided by these connections promotes collaboration and improves the overall efficiency of the verification process.

Benefits of Using UVM Analysis Ports

UVM analysis ports offer several benefits in verification environments. When it comes to promoting modularity, analysis ports play a crucial role. They allow components to interact with each other without the need for direct connections, thus increasing the flexibility and scalability of the verification environment. Instead of relying on intricate and tightly integrated connections, components can communicate through the analysis port. This modularity simplifies the overall design and makes it easier to manage and maintain the testbench.

Another significant advantage of using UVM analysis ports is the enhanced reusability of components. By decoupling the interactions between components, analysis ports allow for easy connection and disconnection of components from the analysis port. This means that components can be reused across multiple verification environments without any modifications, making the development process more efficient. The reusability aspect also enables faster development cycles and reduces overall time spent on creating new verification components.

Furthermore, UVM analysis ports assist in maintaining the desired hierarchy within the verification environment. With analysis ports, higher-level components can interact with lower-level components through a standardized interface. This allows for clear separation of responsibilities and better organization of the testbench infrastructure. Reviewing the hierarchy through analysis ports helps in identifying potential bottlenecks or inefficiencies in the verification process, leading to more effective debugging and optimization.

Data Summary: Benefits of Using UVM Analysis Ports

| Benefit | Explanation |

|---|---|

| Modularity | Components can interact without direct connections, promoting flexibility and scalability. |

| Reusability | Components can be easily connected and disconnected from the analysis port, enabling their reuse across multiple verification environments. |

| Hierarchy | Analysis ports facilitate interaction between higher-level and lower-level components, maintaining a clear and well-organized testbench hierarchy. |

By leveraging the benefits of UVM analysis ports, verification engineers can optimize their verification environments, improve the efficiency of the design process, and achieve more reliable results.

Example Usage of UVM Analysis Ports

UVM analysis ports offer great versatility in different scenarios within a verification environment. Two common examples of their usage include broadcasting transactions and coverage collection.

Broadcasting Transactions

One valuable use case for uvm_analysis_ports is the ability to broadcast transactions from a component to multiple analysis exports. This allows simultaneous receipt and processing of the same transaction across multiple components, enhancing efficiency and enabling collaborative analysis.

Coverage Collection

Another example usage of uvm_analysis_ports is in coverage collection. By connecting a coverage collector component to an analysis port, it becomes possible to receive coverage data from various components in the verification environment. This centralized approach to coverage analysis and reporting simplifies the process and facilitates comprehensive coverage assessment.

| Example Usage | Benefits |

|---|---|

| Broadcasting Transactions | Enables simultaneous transaction processing across multiple components |

| Coverage Collection | Facilitates centralized coverage analysis and reporting |

These examples demonstrate the flexibility and power of uvm_analysis_ports in promoting efficient communication and data exchange within the verification environment.

Best Practices for Using UVM Analysis Ports

When working with UVM analysis ports, it is important to follow best practices to ensure their optimal usage. By incorporating these practices, engineers can enhance the maintainability and performance optimization of their verification environments.

1. Define Analysis Ports and Exports at Appropriate Hierarchy Levels

One best practice is to define analysis ports and exports at appropriate levels of hierarchy within the verification environment. This allows for clear organization and separation of responsibilities between components. By establishing a logical structure, it becomes easier to understand, maintain, and extend the verification environment.

2. Make Connections in the connect_phase() Method

Another best practice is to make connections between analysis ports and exports within the connect_phase() method. This ensures that the connections are established at the appropriate time during simulation. By following this practice, engineers can maintain a structured and predictable initialization process, preventing unexpected issues during the verification process.

3. Avoid Circular Connections

It is important to avoid circular connections between analysis ports and exports. Circular connections can result in an infinite loop of data processing and can lead to simulation issues and poor performance. By carefully designing the connectivity between components, engineers can prevent circular connections and ensure efficient and accurate data analysis.

4. Manage the Number of Connected Exports

To optimize performance, it is crucial to carefully manage the number of connected exports to an analysis port. Connecting excessive exports to a single port can introduce unnecessary overhead and slow down the simulation. By evaluating the requirements of the verification environment and connecting only the necessary exports, engineers can maintain performance while effectively analyzing testbench data.

5. Use the Appropriate Sensitivity List in the imp Class

The imp class, which implements the analysis export, typically includes a sensitivity list. This sensitivity list helps optimize performance by specifying the events or conditions that trigger the analysis export to process incoming transactions. By choosing the appropriate sensitivity list, engineers can ensure that the export responds efficiently to relevant events, reducing unnecessary processing and improving overall performance.

By following these best practices for using UVM analysis ports, engineers can enhance the maintainability of their verification environments, optimize performance, and effectively analyze testbench data.

Conclusion

In conclusion, UVM analysis ports are an integral part of verification environments, playing a crucial role in enabling efficient communication and data exchange between components. By utilizing these ports, engineers can achieve flexibility, modularity, and reusability, leading to enhanced robustness and maintainability of the verification environment.

By following best practices, such as defining analysis ports and exports at appropriate levels of hierarchy and avoiding circular connections, engineers can optimize the usage of UVM analysis ports. Leveraging their capabilities allows for effective analysis of testbench data, leading to improved verification processes.

Overall, UVM analysis ports are a vital component in the arsenal of verification engineers. Their ability to facilitate seamless component interaction and data broadcasting makes them an essential tool for creating robust and efficient verification environments. By mastering the use of UVM analysis ports, engineers can elevate their verification methodologies and achieve better results in their projects.